Hi Team,

Am working on MCAL v8.6.2 for the micro AM263, I have configured SPI0 and SPI1 as CAT2 ISR.

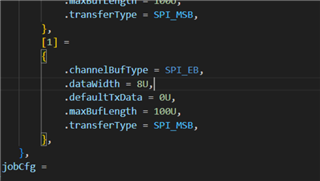

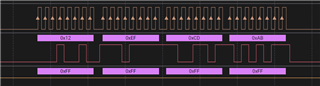

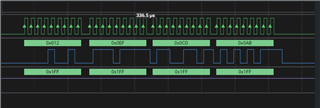

Data width is configured as 8bit for both the channels. attached the snap for your reference.

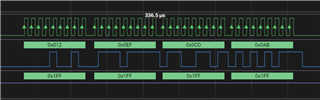

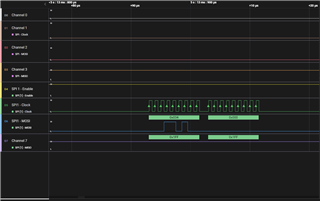

For SPI0 am getting 8bit as it is configured

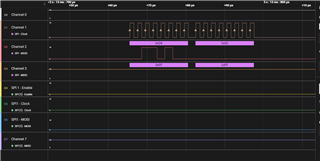

But am getting the 9bit in the logic analyzer for the SPI1.

Could you please let me know where I did the mistake?

Thanks