Hi BU,

In the early thread, I submitted a question about the RBL's behavior after the warm-reset happened at the same time of erasing external Flash. And Aakash proposed that we can reset the Flash via board hardware design, i.e. route the RST pin of Flash device to warm-reset signal of AM263x, so that we can avoid the situation.

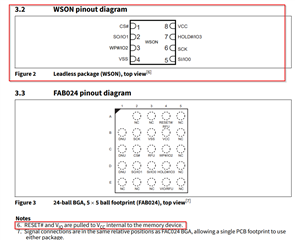

However it is hard to achieve this if the RESET pin for Flash chip is hided by package, for example the following Flash chip:

I replicated the situation with a project and in LaunchPad, the project is attached here: qspi_flash_dma_transfer_am263x-lp_r5fss0-0_nortos_ti-arm-clang.zip

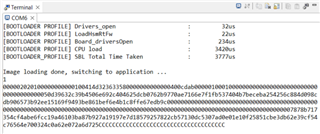

From the serial terminal, you can see that the device now will not boot again:

Please give your further suggestions about this issue.

Regards,

Will