Other Parts Discussed in Thread: HALCOGEN

In our design, we have interfaced SRAM to EMIF interface of TMS570LC4357. It is configured using CS3_N.

On configuring the EMIF for ASYNC2, EMIF clock of 75MHz is seen. Whereas, the CS3_n, OE_n and WE_n signals are not getting generated from TMS570LC4357.

We were reviewing all the E2E Forum queries regarding EMIF interface. In one of the Query, it was answered like "nMPUInit( )" to be included before "EMIFASYN2Init( )".

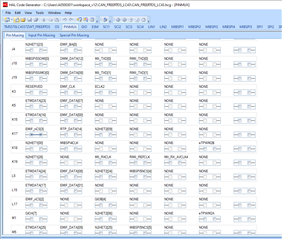

In the Halcogen Tool, on configuring MPU, it is observed that nMPUInit( ) is not getting generated.

We would like to know, is MPUInit(), mandatory? How to configure the same?