I am porting a legacy design to the TM4c129, it has a major piece of code that runs when the FIQ pin is asserted and communicate across the Extended peripheral interface. This must operate uninterrupted, can I switch to FIQ mode, with as little jitter and latency as possible. The main task will use information from this to calculate results for other ports later.

Is the NMI pin a viable option? I'd think this would cause more issues than I'd like.

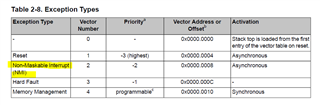

Is setting the priority higher that all interrupts other than faults enough?

Is there any way to externally trigger FIQ mode reliably?