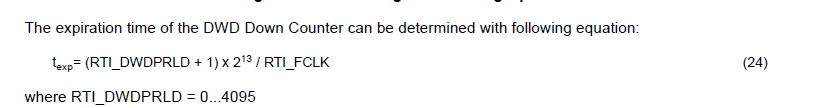

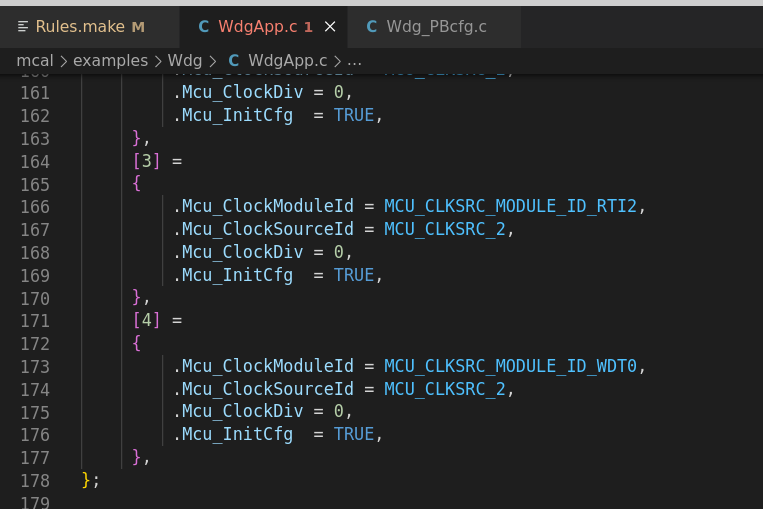

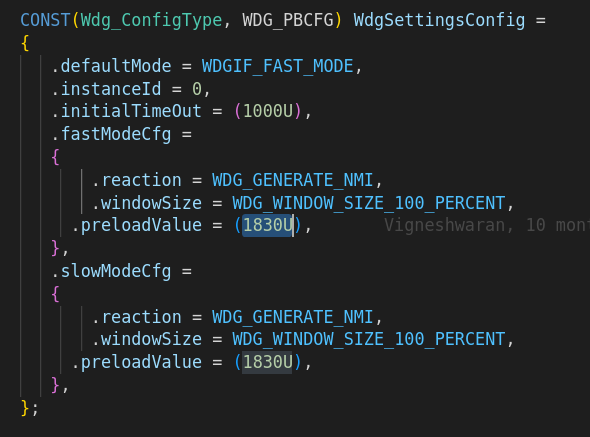

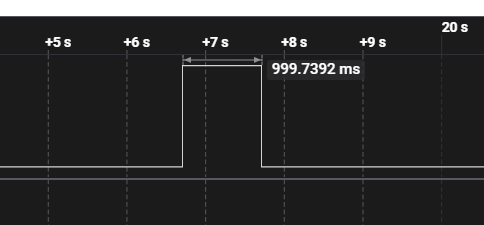

I am currently using MCAL version X.Y.Z how do I configure the WatchDog peripheral to a desired expiry time i.e., After time "t", the WDG must expire and issue a POR reset if not serviced.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.