Other Parts Discussed in Thread: SYSCONFIG

Hi TI Expert,

I am running a multicore project and have a few questions. I am not using lock step mode.

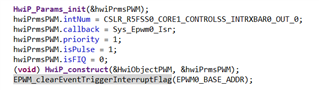

1) The interrupts on core 0 are working fine. Similarly, I have set up interrupt on core 1 and it is not working. Is there a difference in setting interrupts on different cores? should the VIM be set up in "split mode"? if yes, how to set this up?

2) how to sync cores in firmware? Is there a mode setting for this?

3) Is there a way to share data between cores? (for example: is it possible to simply create a global variable which can be easily accessed across multiple cores?). what are the different ways to share data between cores and how to set them up?

Thank you in advance!