Other Parts Discussed in Thread: SYSCONFIG

Hi Team,

I ask this question for our customer:

my custom board mcu is MSPM0L1305, and i use SKD (mspm0_sdk_1_00_00_04) sample to create my keil project. now can download the project into flash, but can not run, the keil log as following:

Set JLink Project File to "C:\ti\L42P-APP\keil\JLinkSettings.ini"* JLink Info: Device "MSPM0L1305" selected.

JLink info:

------------

DLL: V7.82 , compiled Oct 13 2022 13:32:51

Firmware: J-Link V9 compiled May 7 2021 16:26:12

Hardware: V9.30

S/N : 59300616

Feature(s) : RDI, FlashBP, FlashDL, JFlash, GDB

* JLink Info: Found SW-DP with ID 0x6BA02477

* JLink Info: DPIDR: 0x6BA02477

* JLink Info: CoreSight SoC-400 or earlier

* JLink Info: Scanning AP map to find all available APs

* JLink Info: AP[5]: Stopped AP scan as end of AP map has been reached

* JLink Info: AP[0]: AHB-AP (IDR: 0x84770001)

* JLink Info: AP[1]: MEM-AP (IDR: 0x002E0001)

* JLink Info: AP[2]: JTAG-AP (IDR: 0x002E0000)

* JLink Info: AP[3]: MEM-AP (IDR: 0x002E0003)

* JLink Info: AP[4]: MEM-AP (IDR: 0x002E0002)

* JLink Info: Iterating through AP map to find AHB-AP to use

* JLink Info: AP[0]: Core found

* JLink Info: AP[0]: AHB-AP ROM base: 0xF0000000

* JLink Info: CPUID register: 0x410CC601. Implementer code: 0x41 (ARM)

* JLink Info: Found Cortex-M0 r0p1, Little endian.

* JLink Info: FPUnit: 4 code (BP) slots and 0 literal slots

* JLink Info: CoreSight components:

* JLink Info: ROMTbl[0] @ F0000000

* JLink Info: [0][0]: E00FF000 CID B105100D PID 000BB4C0 ROM Table

* JLink Info: ROMTbl[1] @ E00FF000

* JLink Info: [1][0]: E000E000 CID B105E00D PID 000BB008 SCS

* JLink Info: [1][1]: E0001000 CID B105E00D PID 000BB00A DWT

* JLink Info: [1][2]: E0002000 CID B105E00D PID 000BB00B FPB

ROMTableAddr = 0xF0000000

* JLink Info: Reset: Halt core after reset via DEMCR.VC_CORERESET.

* JLink Info: Reset: Reset device via AIRCR.SYSRESETREQ.

Target info:

------------

Device: MSPM0L1305

VTarget = 3.309V

State of Pins: TCK: 0, TDI: 0, TDO: 0, TMS: 1, TRES: 1, TRST: 0

Hardware-Breakpoints: 4

Software-Breakpoints: 8192

Watchpoints: 2

JTAG speed: 4000 kHz

Load "C:\\ti\\L42P-APP\\keil\\Objects\\L42P_APP_FW.axf"

* JLink Info: Reset: Halt core after reset via DEMCR.VC_CORERESET.

* JLink Info: Reset: Reset device via AIRCR.SYSRESETREQ.

*** error 122: AGDI: memory read failed (0x01000020)

* JLink Info: CPU could not be halted

***JLink Error: Cannot read register 15 (R15) while CPU is running

***JLink Error: Cannot read register 16 (XPSR) while CPU is running

***JLink Error: Cannot read register 0 (R0) while CPU is running

***JLink Error: Cannot read register 1 (R1) while CPU is running

***JLink Error: Cannot read register 2 (R2) while CPU is running

***JLink Error: Cannot read register 3 (R3) while CPU is running

***JLink Error: Cannot read register 4 (R4) while CPU is running

***JLink Error: Cannot read register 5 (R5) while CPU is running

***JLink Error: Cannot read register 6 (R6) while CPU is running

***JLink Error: Cannot read register 7 (R7) while CPU is running

***JLink Error: Cannot read register 8 (R8) while CPU is running

***JLink Error: Cannot read register 9 (R9) while CPU is running

***JLink Error: Cannot read register 10 (R10) while CPU is running

***JLink Error: Cannot read register 11 (R11) while CPU is running

***JLink Error: Cannot read register 12 (R12) while CPU is running

***JLink Error: Cannot read register 13 (R13) while CPU is running

***JLink Error: Cannot read register 14 (R14) while CPU is running

***JLink Error: Cannot read register 15 (R15) while CPU is running

***JLink Error: Cannot read register 16 (XPSR) while CPU is running

***JLink Error: Cannot read register 17 (MSP) while CPU is running

***JLink Error: Cannot read register 18 (PSP) while CPU is running

***JLink Error: Cannot read register 20 (CFBP) while CPU is running

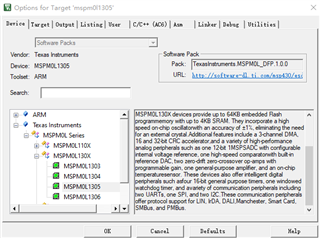

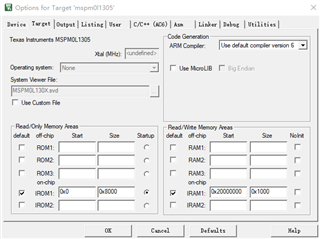

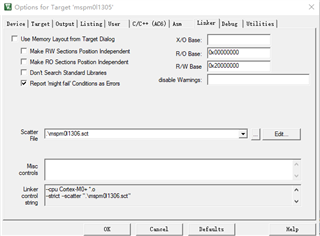

and keil project options as following:

--

Thanks & Regards

Yale