Dear TI Sitara Experts,

we're trying to set the IPC-Mailbox Clusters to some different combination than in the SDK examples (all R5FSS are mapped to CLUSTER0).

We want to deal with separate interrupts on each core, to get the possibility to unmask the correponding interrupts for a single core.

That's because in the near future, two of the R5FSS-Cores shall be running with functional safety code (IEC 61508) and may not be disturbed by unwanted/unexpected interrupts.

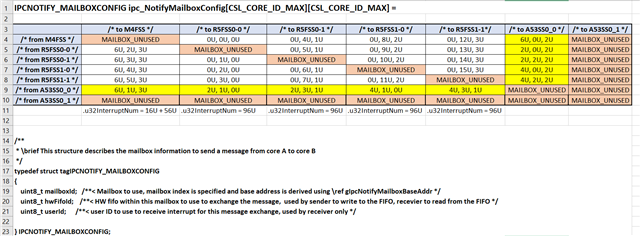

In mcu_plus_sdk_am243x_08_06_00_43 the IPC Notify drivers in file ipc_notify_v0_cfg.c are configured as shown in the following table:

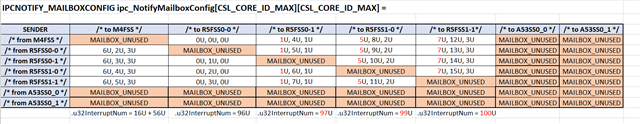

We want to use other Clusters and interrupts combinations instead:

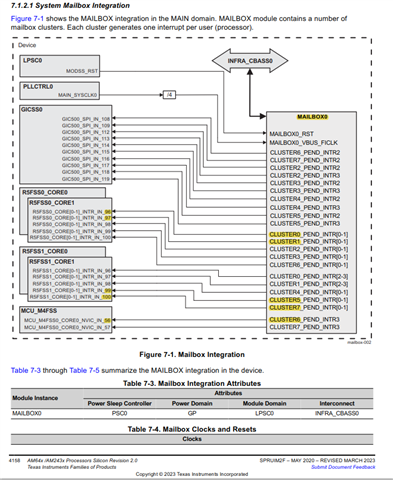

This seems to be possible, as seen in data sheet spruim2f.pdf:

Unfortunately, all other combinations than CLUSTER0 or CLUSTER1 on a R5FSS failed in our trials.

It seems, that internal interrupt 99 or 100 (CLUSTER5 or CLUSTER7) are supressed for somehow.

Is there a special reason for this, or may we take some additional mechanisms in account?

If yes, what combinations would be possible to keep our goal, to have 4 different interrupts on the 4 R4FSS-Cores?

Thanx in advance,

Willi