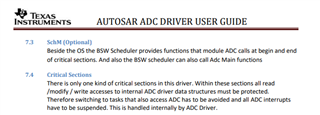

Question 1: As per ADC manual, All adc interrupts needs to be suspended in the critical section.

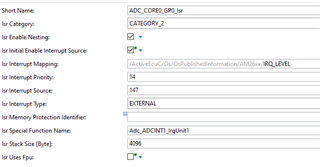

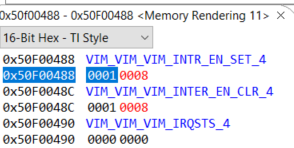

when we suspended all the interrupts inside ADC exclusive area, ADC Interrupts are also not getting triggered.

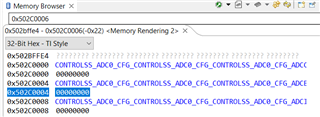

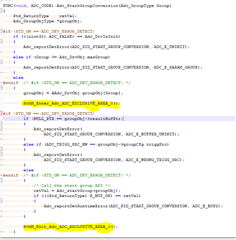

we found in the Adc.c that ADC Start group conversion is happening inside the critical area and we suspended in the configuration as well.

Is it because of the disabling of interrupts inside critical area? Could you please suggest how to implement critical area for ADC?

Question 2:

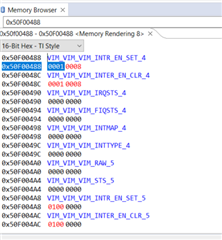

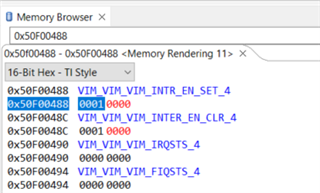

When we modified exclusive area implementation as NONE, that means no interrupts are disabled or enabled, that time ADC interrupts are getting triggered.

But when we start the continuous mode conversion, software always shows OS error and not getting any ADC Interrupt notification, is there anything we need to consider for ADC continuous mode operation?

Do we need to stop the conversion at any time?