Part Number: TMS570LC4357

Hi all,

Please see the attachment file

/** @file HL_sys_startup.c

* @brief Startup Source File

* @date 11-Dec-2018

* @version 04.07.01

*

* This file contains:

* - Include Files

* - Type Definitions

* - External Functions

* - VIM RAM Setup

* - Startup Routine

* .

* which are relevant for the Startup.

*/

/*

* Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/* USER CODE BEGIN (0) */

/* USER CODE END */

/* Include Files */

#include "HL_sys_common.h"

#include "HL_system.h"

#include "HL_sys_vim.h"

#include "HL_sys_core.h"

#include "HL_esm.h"

#include "HL_sys_mpu.h"

#include "HL_errata_SSWF021_45.h"

/* USER CODE BEGIN (1) */

#include "HL_sys_selftest.h"

#include "esm_application_callback.h"

#include "sl_priv.h"

/////////////////////////****************

#include "sl_api.h"

#include "sl_types.h"

#include "HL_errata.h"

#include "HL_reg_dma.h"

#include "HL_reg_can.h"

#include "HL_reg_het.h"

#include "HL_reg_htu.h"

#include "HL_reg_mibspi.h"

#include "HL_reg_adc.h"

#include "HL_reg_efc.h"

#include "HL_reg_stc.h"

#include "HL_reg_pbist.h"

#include "HL_sys_core.h"

//////////////////////////////*************************

/* USER CODE END */

/* USER CODE BEGIN (2) */

volatile uint64 crcAtInit_VIMRAM = 0;

volatile uint64 crcAtInit_FLASH = 0;

/* USER CODE END */

/* External Functions */

/*SAFETYMCUSW 218 S MR:20.2 <APPROVED> "Functions from library" */

extern void __TI_auto_init(void);

/*SAFETYMCUSW 354 S MR:NA <APPROVED> " Startup code(main should be declared by the user)" */

extern int main(void);

/*SAFETYMCUSW 122 S MR:20.11 <APPROVED> "Startup code(exit and abort need to be present)" */

/*SAFETYMCUSW 354 S MR:NA <APPROVED> " Startup code(Extern declaration present in the library)" */

extern void exit(int _status);

//////////////////////////////*************************

extern void muxInit(void);

/* USER CODE BEGIN (3) */

#define STC_ENABLE 1

#define PBIST_ROM_ENABLE 1

#define PBIST_L2RAM_ENABLE 1

#define PBIST_PERIPHRAM_ENABLE 1

#define PBIST_VIM_ENABLE 1

#define L2RAMECCCHECK_ENABLE 0 //fail

#define FLASHECCCHECK_ENABLE 1

#define PERIPHRAMECCCHECK_ENABLE 1

#define EFUSETEST_ENABLE 0 // fail

#define CCMR5TEST_ENABLE 1

//////////////////////////////*************************

/* USER CODE END */

/* USER CODE BEGIN (3) */

void afterSTC(void);

//SL_ResetReason resetReason; /* Reset reason */

/* USER CODE END */

void handlePLLLockFail(void);

/* Startup Routine */

void _c_int00(void);

#define PLL_RETRIES 5U

/* USER CODE BEGIN (4) */

extern uint32 ulHighHandlerLoadStart;

extern uint32 ulHighHandlerLoadEnd;

extern uint32 ulHighHandlerSize;

extern uint32 ulHighHandlerStartAddr;

extern uint32 ulHighHandlerEndAddr;

SL_STC_Config stcSelfTestConfig; /* STC Configuration */

void esmCallBackFunction (uint32 grp_channel, uint32 param1, uint32 param2, uint32 param3);

/* USER CODE END */

#pragma CODE_STATE(_c_int00, 32)

#pragma INTERRUPT(_c_int00, RESET)

#pragma WEAK(_c_int00)

#if 1

void _c_int00(void)

{

register resetSource_t rstSrc;

/* USER CODE BEGIN (5) */

// SL_Init_R5Registers();

//

// /* Initialize Stack Pointers

// * The SL_Init_ResetReason API (and the correspondig HALCoGen getresetsource API) is a C function which uses stack.

// * Stack must be setup correctly before calling this function.*/

// SL_Init_StackPointers();

//

// /* Enable CPU Event Export */

// /* This allows the CPU to signal any single-bit or double-bit errors detected

// * by its ECC logic for accesses to program flash or data RAM.

// */

// /* NOTE - needs to be called on every reset */

// SL_Init_Memory(RAMTYPE_RAM);

// _SL_Init_EnableEventExport();

/* USER CODE END */

/* Reset handler: the following instructions read from the system exception status register

* to identify the cause of the CPU reset.

*/

//rstSrc = getResetSource();

rstSrc = SL_Init_ResetReason();

switch(rstSrc)

{

case POWERON_RESET:

case DEBUG_RESET:

case EXT_RESET:

case RESET_TYPE_DEBUG:

/* USER CODE BEGIN (6) */

/* USER CODE END */

/* Initialize L2RAM to avoid ECC errors right after power on */

_memInit_();

/* USER CODE BEGIN (7) */

/* USER CODE END */

/* Initialize Core Registers to avoid CCM Error */

_coreInitRegisters_();

/* USER CODE BEGIN (8) */

/* USER CODE END */

/* Initialize Stack Pointers */

_coreInitStackPointer_();

/* USER CODE BEGIN (9) */

/* USER CODE END */

/* Enable CPU Event Export */

/* This allows the CPU to signal any single-bit or double-bit errors detected

* by its ECC logic for accesses to program flash or data RAM.

*/

_coreEnableEventBusExport_();

/* USER CODE BEGIN (10) */

/* USER CODE END */

/* Check if there were ESM group3 errors during power-up.

* These could occur during eFuse auto-load or during reads from flash OTP

* during power-up. Device operation is not reliable and not recommended

* in this case. */

if ((esmREG->SR1[2]) != 0U)

{

esmGroup3Notification(esmREG,esmREG->SR1[2]);

}

/* Initialize System - Clock, Flash settings with Efuse self check */

systemInit();

vimInit();

/* USER CODE BEGIN (11) */

SL_ESM_Init(&esmCallBackFunction);

_enable_interrupt_();

mibspiInit();

canInit();

#if (PBIST_ROM_ENABLE == 1) || (PBIST_L2RAM_ENABLE == 1) || (PBIST_PERIPHRAM_ENABLE == 1)

/* Workaround for the Errata PBIST#4 */

errata_PBIST_4();

#endif

#if PBIST_ROM_ENABLE == 1

{

boolean retVal;

/* Start PBIST on STC and PBIST ROM */

retVal = SL_SelfTest_PBIST( PBIST_EXECUTE,

PBIST_RAMGROUP_01_PBIST_ROM |

PBIST_RAMGROUP_02_STC1_1_ROM_R5 |

PBIST_RAMGROUP_03_STC1_2_ROM_R5 |

PBIST_RAMGROUP_04_STC2_ROM_NHET,

PBISTALGO_TRIPLE_READ_FAST_READ |

PBISTALGO_TRIPLE_READ_SLOW_READ);

if(retVal == false){while(1);}

}

#endif

#if EFUSETEST_ENABLE == 1

{

boolean retVal;

SL_EFuse_Config config;

uint32 efcStatus;

config.numPatterns = 600u;

config.seedSignature = 0x5362F97Fu;

config.failInfo.stResult= ST_FAIL;

config.failInfo.failInfo= EFUSE_ERROR_NONE;

efcStatus = efcREG->ERR_STAT;

if(efcStatus == 0x0U)

{

/* Run Stuck At Zero Test (param2=TRUE - Wait for complete) */

retVal = SL_SelfTest_EFuse(EFUSE_SELF_TEST_STUCK_AT_ZERO, TRUE, &config);

if(retVal == false){while(1);}

if(config.failInfo.stResult == ST_PASS)

{

/* Run efuse self test (param2=TRUE - Wait for complete) */

retVal = SL_SelfTest_EFuse(EFUSE_SELF_TEST_ECC, TRUE, &config);

if(retVal == false){while(1);}

if(config.failInfo.stResult != ST_PASS)

{

/* Selftest failed - Class 2 error */

while(1);

}

}

else

{

/* Stuck At Zero test failed - Class 2 error */

while(1);

}

}

else

{

if (efcStatus == 0x15U)

{

/* Run efuse self test (param2=TRUE - Wait for complete) */

retVal = SL_SelfTest_EFuse(EFUSE_SELF_TEST_ECC, TRUE, &config);

if(retVal == false){while(1);}

if(config.failInfo.stResult != ST_PASS)

{

/* Selftest failed - Class 2 error */

while(1);

}

else

{

/* Selftest passed - Class 3 error */

while(1);

}

}

else

{

/* Class 2 error */

while(1);

}

}

}

#endif

#if PBIST_ROM_ENABLE == 1

{

SL_PBIST_FailInfo pbistStatus;

/* Wait for PBIST on ROM to complete */

while(SL_SelfTest_Status_PBIST(&pbistStatus) == FALSE);

SL_SelfTest_PBIST_StopExec();

if(pbistStatus.stResult != ST_PASS)

{

/* PBIST fail */

while(1);

}

/* Clear VIM pending interrupt request (Channel 85 - PBIST Done) */

vimREG->INTREQ2 = 0x00200000;

}

#endif

#if PBIST_L2RAM_ENABLE == 1

{

/* Run PBIST on L2RAM */

SL_SelfTest_PBIST( PBIST_EXECUTE,

PBIST_RAMGROUP_29_L2RAMW |

PBIST_RAMGROUP_30_L2RAMW,

PBISTALGO_MARCH13N_1PORT);

while((systemREG1->MSTCGSTAT & 0x1u) == 0x0u);

if ((pbistREG->FSRF0 == 0u) && (pbistREG->FSRF1 == 0u))

{

/* PBIST pass */

}

else

{

/* PBIST fail */

while(1);

}

SL_SelfTest_PBIST_StopExec();

_memInit_();

/* Clear VIM pending interrupt request (Channel 85 - PBIST Done) */

vimREG->INTREQ2 = 0x00200000;

}

#endif

#if PBIST_PERIPHRAM_ENABLE == 1

{

boolean retVal;

/* Run PBIST on dual port memories (except VIM) */

retVal = SL_SelfTest_PBIST( PBIST_EXECUTE,

PBIST_RAMGROUP_05_AWM1 |

PBIST_RAMGROUP_06_DCAN1 |

PBIST_RAMGROUP_07_DCAN2 |

PBIST_RAMGROUP_08_DMA |

PBIST_RAMGROUP_09_HTU1 |

PBIST_RAMGROUP_10_MIBSPI1 |

PBIST_RAMGROUP_11_MIBSPI2 |

PBIST_RAMGROUP_12_MIBSPI3 |

PBIST_RAMGROUP_13_NHET1 |

PBIST_RAMGROUP_16_RTP |

PBIST_RAMGROUP_18_AWM2 |

PBIST_RAMGROUP_19_DCAN3 |

PBIST_RAMGROUP_20_DCAN4 |

PBIST_RAMGROUP_21_HTU2 |

PBIST_RAMGROUP_22_MIBSPI4 |

PBIST_RAMGROUP_23_MIBSPI5 |

PBIST_RAMGROUP_24_NHET2 |

//PBIST_RAMGROUP_25_FTU | /* Enable only in TMS device */

//PBIST_RAMGROUP_26_FRAY_INBUF_OUTBUF | /* Enable only in TMS device */

PBIST_RAMGROUP_27_CPGMAC_STATE_RXADDR |

PBIST_RAMGROUP_28_CPGMAC_STAT_FIFO,

PBISTALGO_MARCH13N_2PORT);

if(retVal == false){while(1);}

}

#endif

#if L2RAMECCCHECK_ENABLE == 1

{

boolean retVal;

SL_SelfTest_Result result;

retVal = SL_SelfTest_SRAM(SRAM_ECC_ERROR_FORCING_1BIT, TRUE, &result);

if(retVal == false){while(1);}

if(result != ST_PASS)

{

/* Test fail */

while(1);

}

retVal = SL_SelfTest_SRAM(SRAM_ECC_ERROR_FORCING_2BIT, TRUE, &result);

if(retVal == false){while(1);}

if(result != ST_PASS)

{

/* Test fail */

while(1);

}

}

#endif

#if FLASHECCCHECK_ENABLE == 1

{

boolean retVal;

SL_SelfTest_Result result;

/* Flash test needs to be run from a RAM location. Copy flash test to RAM */

uint32 i;

uint32 size=(uint32)&ulHighHandlerSize;

for(i=0;i<size;i++)

{

((char *)&ulHighHandlerStartAddr)[i] =((char *)&ulHighHandlerLoadStart)[i];

}

_SL_HoldNClear_nError();

retVal = SL_SelfTest_Flash(FLASH_ECC_TEST_MODE_1BIT, TRUE, &result);

if(retVal == false){while(1);}

if(result != ST_PASS)

{

/* Test fail */

while(1);

}

retVal = SL_SelfTest_Flash(FLASH_ECC_TEST_MODE_2BIT, TRUE, &result);

if(retVal == false){while(1);}

if(result != ST_PASS)

{

/* Test fail */

while(1);

}

}

#endif

#if PBIST_PERIPHRAM_ENABLE == 1

{

SL_PBIST_FailInfo pbistStatus;

while(SL_SelfTest_Status_PBIST(&pbistStatus) == FALSE);

SL_SelfTest_PBIST_StopExec();

if(pbistStatus.stResult != ST_PASS)

{

/* PBIST fail */

while(1);

}

/* Clear VIM pending interrupt request (Channel 85 - PBIST Done) */

vimREG->INTREQ2 = 0x00200000;

/* Memory Init for MIBSPI */

mibspiREG1->GCR0 = 0x1U;

mibspiREG2->GCR0 = 0x1U;

mibspiREG3->GCR0 = 0x1U;

mibspiREG4->GCR0 = 0x1U;

mibspiREG5->GCR0 = 0x1U;

while ((mibspiREG1->FLG & 0x01000000U) == 0x01000000U)

{

}/* Wait */

mibspiREG1->MIBSPIE = 1;

mibspiREG1->PAR_ECC_CTRL = (mibspiREG1->PAR_ECC_CTRL & 0xFFFFFFF0) | 0xA;

while ((mibspiREG2->FLG & 0x01000000U) == 0x01000000U)

{

}/* Wait */

mibspiREG2->MIBSPIE = 1;

mibspiREG2->PAR_ECC_CTRL = (mibspiREG2->PAR_ECC_CTRL & 0xFFFFFFF0) | 0xA;

while ((mibspiREG3->FLG & 0x01000000U) == 0x01000000U)

{

}/* Wait */

mibspiREG3->MIBSPIE = 1;

mibspiREG3->PAR_ECC_CTRL = (mibspiREG3->PAR_ECC_CTRL & 0xFFFFFFF0) | 0xA;

while ((mibspiREG4->FLG & 0x01000000U) == 0x01000000U)

{

}/* Wait */

mibspiREG4->MIBSPIE = 1;

mibspiREG4->PAR_ECC_CTRL = (mibspiREG4->PAR_ECC_CTRL & 0xFFFFFFF0) | 0xA;

while ((mibspiREG5->FLG & 0x01000000U) == 0x01000000U)

{

}/* Wait */

mibspiREG5->MIBSPIE = 1;

mibspiREG5->PAR_ECC_CTRL = (mibspiREG5->PAR_ECC_CTRL & 0xFFFFFFF0) | 0xA;

/* Enable ECC for other RAMs */

dmaREG->DMAPCR = 0xA;

hetREG1->PCR = 0xA;

htuREG1->PCR = 0xA;

hetREG2->PCR = 0xA;

htuREG2->PCR = 0xA;

canREG1->CTL = (canREG1->CTL & 0xFFFFC3FF) | (0xA << 10);

canREG2->CTL = (canREG2->CTL & 0xFFFFC3FF) | (0xA << 10);

canREG3->CTL = (canREG3->CTL & 0xFFFFC3FF) | (0xA << 10);

canREG4->CTL = (canREG4->CTL & 0xFFFFC3FF) | (0xA << 10);

adcREG1->PARCR = 0xA;

adcREG2->PARCR = 0xA;

/* Memory Init for all RAMs (except VIM) with correct ECC */

SL_Init_Memory( RAMTYPE_DMA_RAM |

RAMTYPE_NHET1 |

RAMTYPE_HET_TU1 |

RAMTYPE_NHET2 |

RAMTYPE_HET_TU2 |

RAMTYPE_DCAN1_RAM |

RAMTYPE_DCAN2_RAM |

RAMTYPE_DCAN3_RAM |

RAMTYPE_DCAN4_RAM |

RAMTYPE_MIBSPI1_RAM |

RAMTYPE_MIBSPI2_RAM |

RAMTYPE_MIBSPI3_RAM |

RAMTYPE_MIBSPI4_RAM |

RAMTYPE_MIBSPI5_RAM |

RAMTYPE_MIBADC1_RAM |

RAMTYPE_MIBADC2_RAM );

}

#endif

#if PERIPHRAMECCCHECK_ENABLE == 1

{

// canInit();

// //

// // /* Initialise CAN SRAM */

// SL_Init_Memory(RAMTYPE_DCAN1_RAM);

// SL_Init_Memory(RAMTYPE_DCAN2_RAM);

// SL_Init_Memory(RAMTYPE_DCAN3_RAM);

// SL_Init_Memory(RAMTYPE_DCAN4_RAM);

_SL_HoldNClear_nError();

if(SL_SelfTest_CAN(CAN_ECC_TEST_MODE_1BIT, SL_DCAN1) == false)

{

while(1);

}

if(SL_SelfTest_CAN(CAN_ECC_TEST_MODE_2BIT, SL_DCAN1) == false)

{

while(1);

}

// if(SL_SelfTest_CAN(CAN_ECC_TEST_MODE_1BIT, SL_DCAN2) == false)

// {

// while(1);

// }

// if(SL_SelfTest_CAN(CAN_ECC_TEST_MODE_2BIT, SL_DCAN2) == false)

// {

// while(1);

// }

// if(SL_SelfTest_CAN(CAN_ECC_TEST_MODE_1BIT, SL_DCAN3) == false)

// {

// while(1);

// }

// if(SL_SelfTest_CAN(CAN_ECC_TEST_MODE_2BIT, SL_DCAN3) == false)

// {

// while(1);

// }

// if(SL_SelfTest_CAN(CAN_ECC_TEST_MODE_1BIT, SL_DCAN4) == false)

// {

// while(1);

// }

// if(SL_SelfTest_CAN(CAN_ECC_TEST_MODE_2BIT, SL_DCAN4) == false)

// {

// while(1);

// }

if(SL_SelfTest_DMA(DMA_ECC_TEST_MODE_1BIT) == false)

{

while(1);

}

if(SL_SelfTest_DMA(DMA_ECC_TEST_MODE_2BIT) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_1BIT, SL_MIBSPI1) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_2BIT, SL_MIBSPI1) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_1BIT, SL_MIBSPI2) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_2BIT, SL_MIBSPI2) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_1BIT, SL_MIBSPI3) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_2BIT, SL_MIBSPI3) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_1BIT, SL_MIBSPI4) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_2BIT, SL_MIBSPI4) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_1BIT, SL_MIBSPI5) == false)

{

while(1);

}

if(SL_SelfTest_MibSPI(MIBSPI_ECC_TEST_MODE_2BIT, SL_MIBSPI5) == false)

{

while(1);

}

}

#endif

#if CCMR5TEST_ENABLE == 1

{

boolean retVal;

SL_CCMR5F_FailInfo failInfo;

retVal = SL_SelfTest_CCMR5F(CCMR5F_CPUCOMP_SELF_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_CPUCOMP_ERROR_FORCING_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_CPUCOMP_SELF_TEST_ERROR_FORCING, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_VIMCOMP_SELF_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_VIMCOMP_ERROR_FORCING_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_VIMCOMP_SELF_TEST_ERROR_FORCING, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_PDCOMP_SELF_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_VIMCOMP_ERROR_FORCING_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_VIMCOMP_SELF_TEST_ERROR_FORCING, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_PDCOMP_SELF_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_PDCOMP_ERROR_FORCING_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_PDCOMP_SELF_TEST_ERROR_FORCING, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_INMCOMP_SELF_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_INMCOMP_ERROR_FORCING_TEST, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

retVal = SL_SelfTest_CCMR5F(CCMR5F_INMCOMP_SELF_TEST_ERROR_FORCING, TRUE, &failInfo);

if(retVal == false){while(1);}

if(failInfo.stResult != ST_PASS)

{

while(1);

}

}

#endif

#if PBIST_VIM_ENABLE == 1

{

boolean retVal;

SL_PBIST_FailInfo pbistStatus;

/* Start PBIST on STC and PBIST ROM */

retVal = SL_SelfTest_PBIST( PBIST_EXECUTE,

PBIST_RAMGROUP_01_PBIST_ROM |

PBIST_RAMGROUP_02_STC1_1_ROM_R5 |

PBIST_RAMGROUP_03_STC1_2_ROM_R5 |

PBIST_RAMGROUP_04_STC2_ROM_NHET,

PBISTALGO_TRIPLE_READ_FAST_READ |

PBISTALGO_TRIPLE_READ_SLOW_READ);

if(retVal == false){while(1);}

/* Wait for PBIST on ROM to complete */

while(SL_SelfTest_Status_PBIST(&pbistStatus) == FALSE);

SL_SelfTest_PBIST_StopExec();

if(pbistStatus.stResult != ST_PASS)

{

/* PBIST fail */

while(1);

}

/* Clear VIM pending interrupt request (Channel 85 - PBIST Done) */

vimREG->INTREQ2 = 0x00200000;

}

#endif

/* USER CODE END */

/* Enable IRQ offset via Vic controller */

_coreEnableIrqVicOffset_();

/* Initialize VIM table */

vimInit();

/* USER CODE BEGIN (12) */

/* USER CODE END */

/* Configure system response to error conditions signaled to the ESM group1 */

/* This function can be configured from the ESM tab of HALCoGen */

esmInit();

/* USER CODE BEGIN (13) */

#if STC_ENABLE == 1

{

SL_STC_Config stcSelfTestConfig;

stcSelfTestConfig.stcClockDiv = 2; /* STC Clock divider = 1 */

stcSelfTestConfig.intervalCount = 1; /* One interval only */

stcSelfTestConfig.restartInterval0 = TRUE; /* Start from interval 0 */

stcSelfTestConfig.timeoutCounter = 0xFFFFFFFF; /* Timeout counter*/

SL_SelfTest_STC(STC1_COMPARE_SELFCHECK, TRUE, &stcSelfTestConfig);

while(1); /* STC failed to start */

}

#endif

/* USER CODE END */

break;

case OSC_FAILURE_RESET:

/* USER CODE BEGIN (14) */

/* USER CODE END */

break;

case WATCHDOG_RESET:

/* USER CODE BEGIN (15) */

/* USER CODE END */

break;

case RESET_TYPE_CPU0:

case RESET_TYPE_CPU1:

/* USER CODE BEGIN (16) */

/* USER CODE END */

/* Initialize Core Registers to avoid CCM Error */

_coreInitRegisters_();

/* USER CODE BEGIN (17) */

/* USER CODE END */

/* Initialize Stack Pointers */

_coreInitStackPointer_();

/* USER CODE BEGIN (18) */

/* USER CODE END */

/* Enable CPU Event Export */

/* This allows the CPU to signal any single-bit or double-bit errors detected

* by its ECC logic for accesses to program flash or data RAM.

*/

_coreEnableEventBusExport_();

/* USER CODE BEGIN (19) */

#if STC_ENABLE == 1

if ((stcREG1->STCSCSCR & 0xFU) == 0xAU)

{

/* check if the self-test fail bit is set */

if ((stcREG1->STCGSTAT & 0x3U) != 0x3U)

{

/* STC self-check has failed */

while(1);

}

/* STC self-check has passed */

else

{

/* clear self-check mode */

stcREG1->STCSCSCR = 0x05U;

/* clear STC global status flags */

stcREG1->STCGSTAT = 0x3U;

/* clear ESM group1 channel 27 status flag */

esmREG->SR1[0U] = 0x08000000U;

{

SL_STC_Config stcSelfTestConfig;

stcSelfTestConfig.stcClockDiv = 0; /* STC Clock divider = 1 */

stcSelfTestConfig.intervalCount = 1; /* One interval only */

stcSelfTestConfig.restartInterval0 = TRUE; /* Start from interval 0 */

stcSelfTestConfig.timeoutCounter = 0xFFFFFFFF; /* Timeout counter*/

SL_SelfTest_STC(STC1_RUN, TRUE, &stcSelfTestConfig);

while(1); /* STC failed to start */

}

}

}

/* CPU reset caused by CPU self-test completion */

else if ((stcREG1->STCGSTAT & 0x1U) == 0x1U)

{

/* Self-Test Fail flag is set */

if ((stcREG1->STCGSTAT & 0x2U) == 0x2U)

{

/* Call CPU self-test failure handler */

while(1);

}

/* CPU self-test completed successfully */

else

{

/* clear STC global status flag */

stcREG1->STCGSTAT = 0x1U;

/* Continue start-up sequence after CPU STC completed */

}

}

/* CPU reset caused by software writing to CPU RESET bit */

else

{

/* Add custom routine here to handle the case where software causes CPU reset */

}

#endif

/* USER CODE END */

break;

case SW_RESET:

/* USER CODE BEGIN (20) */

/* USER CODE END */

break;

default:

/* USER CODE BEGIN (21) */

/* USER CODE END */

break;

}

/* USER CODE BEGIN (22) */

/* USER CODE END */

_mpuInit_();

/* USER CODE BEGIN (23) */

/* USER CODE END */

_cacheEnable_();

/* USER CODE BEGIN (24) */

/* USER CODE END */

/* USER CODE BEGIN (25) */

/* USER CODE END */

/* initialize global variable and constructors */

__TI_auto_init();

/* USER CODE BEGIN (26) */

/* USER CODE END */

/* call the application */

/*SAFETYMCUSW 296 S MR:8.6 <APPROVED> "Startup code(library functions at block scope)" */

/*SAFETYMCUSW 326 S MR:8.2 <APPROVED> "Startup code(Declaration for main in library)" */

/*SAFETYMCUSW 60 D MR:8.8 <APPROVED> "Startup code(Declaration for main in library;Only doing an extern for the same)" */

_CPU_system_mode_Switch(); // for testing mode switching

main();

/* USER CODE BEGIN (27) */

/* USER CODE END */

/*SAFETYMCUSW 122 S MR:20.11 <APPROVED> "Startup code(exit and abort need to be present)" */

exit(0);

}

/* USER CODE BEGIN (28) */

/* USER CODE END */

boolean pll1_slip_faultinject_callback1 = FALSE;

boolean pll2_slip_faultinject_callback2 = FALSE;

extern uint32 callbkParam1, callbkParam2, callbkParam3, callbkParam4, callbkParam5, callbkParam6;

/* USER CODE BEGIN (29) */

void esmCallBackFunction (uint32 grp_channel, uint32 param1, uint32 param2, uint32 param3)

{

volatile uint32 flashread = 0u;

/********************************************************************************************************/

/*all GROUP 1 errors are captured here*/

/********************************************************************************************************/

#if defined(_TMS570LC43x_) || defined(_RM57Lx_)

uint32 channel;

channel = grp_channel & 0xffffu;

if ((grp_channel & ESM_GRP1_MASK) == ESM_GRP1_MASK)

{

/* process group 1 callbacks */

if (ESM_G1ERR_DMA_ECC_SBERR == channel)

{

/* Clear flags and read error address */

BIT_SET(dmaREG->DMASECCCTRL, BIT(DMA_ECC_SBERR));

/* Clear ESM error status */

esmREG->SR7[0] = GET_ESM_BIT_NUM(ESM_G1ERR_DMA_ECC_SBERR);

dma_1bit_faultinject_callback = TRUE;

}

else if (ESM_G1ERR_DMA_ECC_UNCORR == channel)

{

/* Clear flags and read error address */

BIT_SET(dmaREG->DMAPAR, BIT(DMA_ECC_ERR));

/* Clear ESM error status */

esmREG->SR1[0] = GET_ESM_BIT_NUM(ESM_G1ERR_DMA_ECC_UNCORR);

dma_2bit_faultinject_callback = TRUE;

}

else if ((ESM_G1ERR_CAN1_ECC_SBERR == channel) ||

(ESM_G1ERR_CAN2_ECC_SBERR == channel) ||

(ESM_G1ERR_CAN3_ECC_SBERR == channel) ||

(ESM_G1ERR_CAN4_ECC_SBERR == channel))

{

/* Clear ESM error status */

esmREG->SR7[0] = GET_ESM_BIT_NUM(channel);

can_1bit_faultinject_callback = TRUE;

}

else if ((ESM_G1ERR_CAN1_ECC_UNCORR == channel) ||

(ESM_G1ERR_CAN2_ECC_UNCORR == channel) ||

(ESM_G1ERR_CAN3_ECC_UNCORR == channel))

{

/* Clear ESM error status */

esmREG->SR1[0] = GET_ESM_BIT_NUM(channel);

can_2bit_faultinject_callback = TRUE;

}

else if ((ESM_G1ERR_CAN4_ECC_UNCORR == channel))

{

esmREG->SR4[0] = GET_ESM_BIT_NUM(channel);

can_2bit_faultinject_callback = TRUE;

}

else if ((ESM_G1ERR_SPI1_ECC_SBERR == channel) ||

(ESM_G1ERR_SPI2_ECC_SBERR == channel) ||

(ESM_G1ERR_SPI3_ECC_SBERR == channel) ||

(ESM_G1ERR_SPI4_ECC_SBERR == channel) ||

(ESM_G1ERR_SPI5_ECC_SBERR == channel))

{

/* Clear ESM error status */

esmREG->SR7[0] = GET_ESM_BIT_NUM(channel);

mibspi_1bit_faultinject_callback = TRUE;

}

else if ((ESM_G1ERR_SPI1_ECC_UNCORR == channel) ||

(ESM_G1ERR_SPI3_ECC_UNCORR == channel) ||

(ESM_G1ERR_SPI5_ECC_UNCORR == channel))

{

/* Clear ESM error status */

esmREG->SR1[0] = GET_ESM_BIT_NUM(channel);

mibspi_2bit_faultinject_callback = TRUE;

}

else if ((ESM_G1ERR_SPI2_ECC_UNCORR == channel) ||

(ESM_G1ERR_SPI4_ECC_UNCORR == channel))

{

esmREG->SR4[0] = GET_ESM_BIT_NUM(channel);

mibspi_2bit_faultinject_callback = TRUE;

}

else if (ESM_G1ERR_CCMR5_SELFTEST == channel)

{

esmREG->SR1[0] = GET_ESM_BIT_NUM(channel);

/* no need to set the flag cccmr5f_errorforcing_app_callback, as the

* flag is already set by the G2 error */

}

else if (ESM_G1ERR_PSCON_COMPARE_ERR == channel)

{

/*clear nerror and esm flags*/

esmREG->SR4[0] |= GET_ESM_BIT_NUM(ESM_G1ERR_PSCON_COMPARE_ERR);

esmREG->SR4[0] |= GET_ESM_BIT_NUM(ESM_G1ERR_PSCON_SELTEST_ERR);

_SL_HoldNClear_nError();

pscon_errorforcing_app_callback = TRUE;

}

else if (ESM_G1ERR_PSCON_SELTEST_ERR == channel)

{

/*clear nerror and esm flags*/

esmREG->SR4[0] |= GET_ESM_BIT_NUM(ESM_G1ERR_PSCON_SELTEST_ERR);

_SL_HoldNClear_nError();

pscon_selftest_errorforcing_app_callback = TRUE;

}

else if(ESM_G1ERR_PLL1_SLIP == channel)

{

callbkParam1 = param1 & (uint32)0x1u;

callbkParam2 = param1 & (uint32)0x2u;

esmREG->SR1[0] |= GET_ESM_BIT_NUM(ESM_G1ERR_PLL1_SLIP);

pll1_slip_faultinject_callback1 = TRUE;

}

else if(ESM_G1ERR_PLL2_SLIP == channel)

{

callbkParam1 = param1 & (uint32)0x1u;

callbkParam2 = param1 & (uint32)0x2u;

esmREG->SR4[0] |= GET_ESM_BIT_NUM(ESM_G1ERR_PLL2_SLIP);

pll2_slip_faultinject_callback2 = TRUE;

}

}

if ((grp_channel & ESM_GRP2_MASK) == ESM_GRP2_MASK)

{

/* process group 2 call-backs */

if ((ESM_G2ERR_CCMR5_CPUCOMP_ERR == channel) ||

(ESM_G2ERR_CCMR5_VIMCOMP_ERR == channel) ||

(ESM_G2ERR_CCMR5_INMCOMP_ERR == channel) ||

(ESM_G2ERR_CCMR5_PDCOMP_ERR == channel))

{

esmREG->SSR2 = GET_ESM_BIT_NUM(channel);

/* Clear nError */

_SL_HoldNClear_nError();

cccmr5f_errorforcing_app_callback = TRUE;

}

}

#endif

}

#endif

/* USER CODE END */

/* USER CODE END */

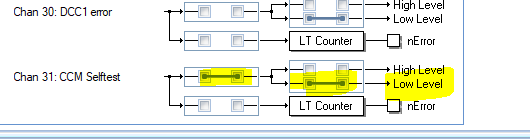

In this file we are using safeTI dignostic features but we are facing some issue here

In line no. 634 --> retVal = SL_SelfTest_CCMR5F(CCMR5F_CPUCOMP_SELF_TEST_ERROR_FORCING, TRUE, &failInfo); this function is failing.

It is failing inside static void sl_esm_high_intr_handler(void) function in sl_esm.c file.

inside this function

esmOffH = (uint8) esmREG->IOFFHR; "value of this register is 0x24"

I think the value of above register is not correct out if range "35-32 = 3 which is not in switch case ".

Please see and let me know why this ECC test case is failing and also see my attached file.

Thanks

Pankaj Verma