Part Number: MSPM0L1304

Hi,

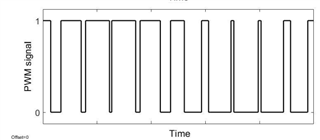

My customer is using DMA to set duty of PWM.

He needs 3ch PWM and this requires 3ch DMA.

However, MSPM0 only supports 1 full-feature channel (DMA0), supporting repeated transfer modes.

Repeated transfer mode is required to use DMA for PWM duty setting.

So the customer wants to use the three PWM duty register to alternate with the DMA0 channel.

The destination address of DMA0 rotates repeatedly in the order of PWM0, PWM1, PWM2, PWM0.

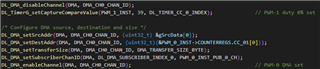

When setting up DMA, he is trying to do the code below.

Repeat the routine below.

{

// Configure DMA for PWM0

Disable DMA

DMA setting

DL_DMA_setDestAddr(DMA, DMA_CH0_CHAN_ID, PWM_0CH_duty_reg_addr)

Enable DMA

// Configure DMA for PWM1

Disable DMA

DMA Setting

DL_DMA_setDestAddr(DMA, DMA_CH0_CHAN_ID, PWM_1CH_duty_reg_addr)

Enable DMA

// Configure DMA for PWM2

Disable DMA

DMA setting

DL_DMA_setDestAddr(DMA, DMA_CH0_CHAN_ID, PWM_2CH_duty_reg_addr)

Enable DMA

}

Is this concept possible?

And does this concept increase the CPU burden?

Thanks.