Other Parts Discussed in Thread: HALCOGEN

Hi,

The SAFETI-HALCOGEN-CSP provides a number of unit tests for the RTI module (RTI_UT_01:1 to RTI_UT_21:1).

I have found that if I try to run all of these tests then RTI_UT_21:1 never terminates.

The console output is as follows:

********************************************************************************** Executing Existing Test Case 57 in Sequence RTI_UT* File : D:\MCU_FSIM\OM-8857\code\src\OM_MCU_FSIM_SwSolution\OM_MCU_FSIM_SwSolution\code\src\HAL\source\HL_rti.c* Procedure : rtiInit*********************************************************************************

Call rtiInit No exception raised

But I have also found that if I do not run RTI_UT_01:1 then RTI_UT_21:1 does terminate successfully.

Question 1: Do you know why running RTI_UT_01:1 prevents RTI_UT_21:1 from terminating.

The start-up code in RTI_UT.xlsx is

/* Run RTI on oscillator to reduce the clock speed */

systemREG1->RCLKSRC = 0;

Question 2: Why is this necessary?

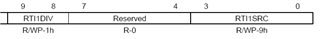

As well as setting the clock source to Oscillator this sets the RTICLK1 divider value to 1.

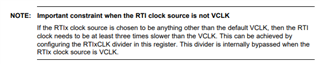

But the note in section 2.5.1.18 of the Technical Reference Manual (spnu563a) states the following.

Question 3: Aren't these unit tests violating this constraint?

Thank you,

Andrew