Part Number: MSPM0L1306

Other Parts Discussed in Thread: TIGER

Hi there,

We are designing a device (fuel gauge) using MSPM0L1306 controller, and set the I2C0 in target mode, using PA0 & PA1 pins (which don't have internal pull-up resistors, for 5v tolerant). We don't deploy pull-up resistors on the target (self) side, the pull-up resistor is only present on the host side (to fit any resonible IO voltage).

We observed that if clock stretching is enabled, the SCL pin will be hold low permanently by MSPM0L1306. This prevent our host side to communicate with target, and block the further functionality.

Do you know how can we design a mechanism to let MSPM0L1306 distinguish the target disconnection from host device (pull-up resistor disappear)? And recover the communication once it plugged to host device (with correct pull-up resistors)?

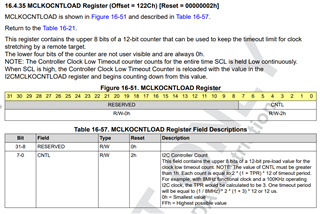

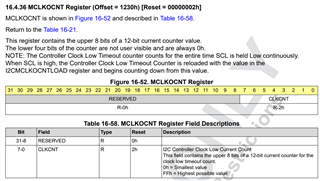

Also, in reference manual 16.2.3.6, the register name I2Cx.MCLKOCNTLOAD doesn't exist in the later I2c registers chapter. Maybe another name? (manual typo)

Bests,