Hi BU,

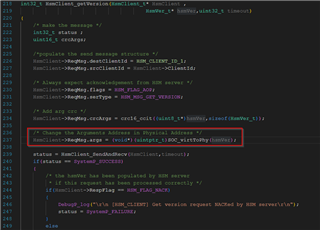

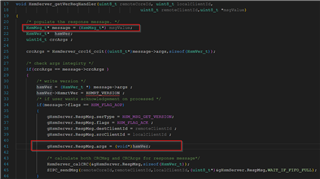

We use Secure IPC to get HSM service, and the data transfer is via pointer as below. For data transfer from R5F to M4, it is ok; but for data transfer from M4 to R5F, and if R5F using cache, there might be problem. I want to know the handle for cache coherency. Do you think in SDK we should add some operation to void the possible problem?

Regards,

Will