Part Number: TMS570LS1224

Other Parts Discussed in Thread: HALCOGEN

I've never used TI FEE, but as I started using it this time, I had a few questions.

It would be very helpful if you answered yes or no to my question.

1. The purpose of BANK 7 provided by TMS570LS1224 is 64KB FLASH area to use EEPROM function rather than physical EEPROM, right?

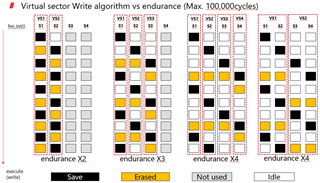

2. The reason why at least two virtual sectors are required is to erase and write in block units to compensate for the disadvantage of FLASH, which has to be erased and written in sector units?

3. Another purpose of having virtual sectors is to extend the limited write life of 100,000 cycles?

4. After executing TI_Fee_WriteAsync(), the block must be invalidated using TI_Fee_InvalidateBlock() for the next write?

5. Do I have to do read and invalidate after write?

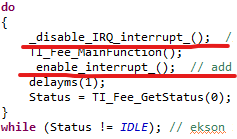

6. Is it correct to run disable irq when executing Write and InvalidateBlock asynchronously? (If disable_irq is not performed, the problem of receiving prefetchEntry of sys_intvecs.asm occurs intermittently, and the same disable_irq is performed when using the F021 flash write function)

7. In the case of 64KB BANK 7 (4 sectors), is it correct to operate as shown in the figure below when writing -> reading -> invalidating is repeated according to the number of VS (virtual sectors) settings?