Other Parts Discussed in Thread: HALCOGEN

Hi,

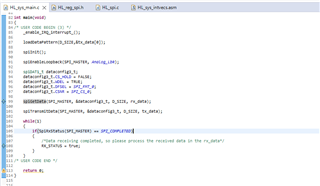

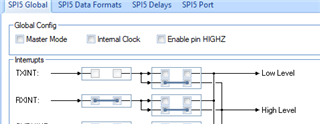

I am trying to use the SPI5 RX interrupt in Halcogen/CCS project,

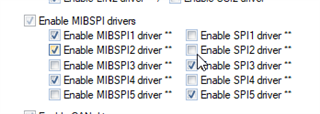

SPI 5 is not in MibSPi mode:

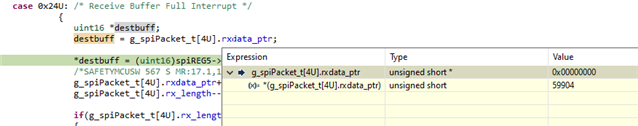

The interrupt routine is called:

Here the programm crashes because it makes use of a NULL pointer. This seems to be related to MibSpi, why is that invalid code generated and called?

I attached to project if it helps.

Best Regards

Juergen