Other Parts Discussed in Thread: HALCOGEN,

Hello, team.

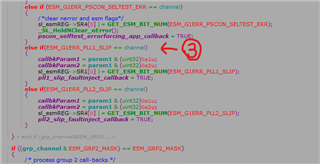

According to Safety Manual (SPNU575A), I implemented PLL1 Slip detector (CLK2).

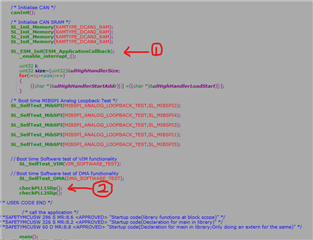

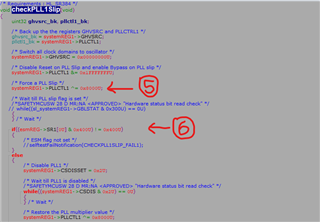

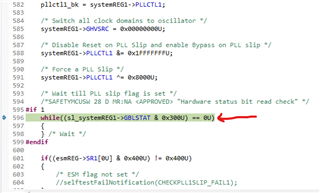

I copied checkPLL1Slip() anc checkPLL2Slip() from TI Sample code in demo_app (..\SafeTI Diagnostic Library\2.4.0\demo_app\common\source\faultInject.c).

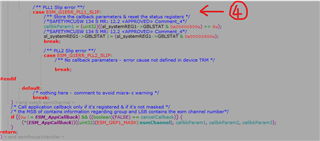

However, System halt occurs in checkPLL1Slip().

checkPLL2Slip() is not problem.

It's my setupPLL() code.

void setupPLL(void)

{

/* USER CODE BEGIN (3) */

/* USER CODE END */

/* Disable PLL1 and PLL2 */

systemREG1->CSDISSET = 0x00000002U | 0x00000040U;

/*SAFETYMCUSW 28 D MR:NA <APPROVED> "Hardware status bit read check" */

while((systemREG1->CSDIS & 0x42U) != 0x42U)

{

/* Wait */

}

/* Clear Global Status Register */

systemREG1->GBLSTAT = 0x301U;

/** - Configure PLL control registers */

/** @b Initialize @b Pll1: */

/** - Setup pll control register 1:

* - Setup reset on oscillator slip

* - Setup bypass on pll slip

* - setup Pll output clock divider to max before Lock

* - Setup reset on oscillator fail

* - Setup reference clock divider

* - Setup Pll multiplier

*/

systemREG1->PLLCTL1 = (uint32)0x00000000U

| (uint32)0x20000000U

| (uint32)((uint32)0x1FU << 24U)

| (uint32)0x00000000U

| (uint32)((uint32)(8U - 1U)<< 16U)

| (uint32)(0xA400U);

/** - Setup pll control register 2

* - Setup spreading rate

* - Setup bandwidth adjustment

* - Setup internal Pll output divider

* - Setup spreading amount

*/

systemREG1->PLLCTL2 = (uint32)((uint32)255U << 22U)

| (uint32)((uint32)7U << 12U)

| (uint32)((uint32)(1U - 1U) << 9U)

| (uint32)61U;

/** @b Initialize @b Pll2: */

/** - Setup pll2 control register :

* - setup Pll output clock divider to max before Lock

* - Setup reference clock divider

* - Setup internal Pll output divider

* - Setup Pll multiplier

*/

systemREG2->PLLCTL3 = (uint32)((uint32)(1U - 1U) << 29U)

| (uint32)((uint32)0x1FU << 24U)

| (uint32)((uint32)(8U - 1U)<< 16U)

| (uint32)(0xA400U);

/** - Enable PLL(s) to start up or Lock */

systemREG1->CSDIS = 0x00000000U

| 0x00000000U

| 0x00000008U

| 0x00000080U

| 0x00000000U

| 0x00000000U

| 0x00000000U

| 0x00000004U;

}

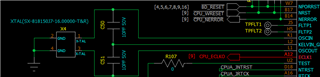

My board is Custom board. (Not evaluation board)

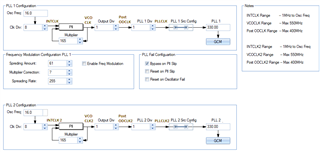

Below is PLL Setting in Halcogen.

Please let me know where the wrong is.

Best regard.

Gene.