Hello,

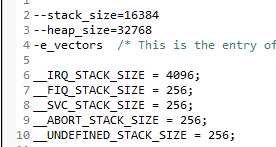

After running my multi-core program, Core 1 has a Prefetch Abort Exception (PABT) as shown by offset 0xC in the exception table:

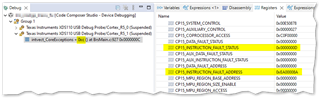

The reason is because there is an attempt to execute an instruction located in non-existent memory, address 0xEA0008A, shown in the IFAR:

I guess it could be a corrupt function pointer and fortunately it is always the same problem address.

In the case of an MPU error or Undefined Instruction exception, the IFAR would contain the address of the offending instruction (I think) which I could look up in the map file to see in which input section the problem was located. But in this case, it is the instruction address itself that is non-existent.

How can I determine the point in my program which immediately precedes the fetch from the non-existent address please? Any tips would be appreciated. The debugging guide (SPRAD28) gives no advice on this specific situation.