Other Parts Discussed in Thread: HALCOGEN

Transmit Buffer Empty Interrupt

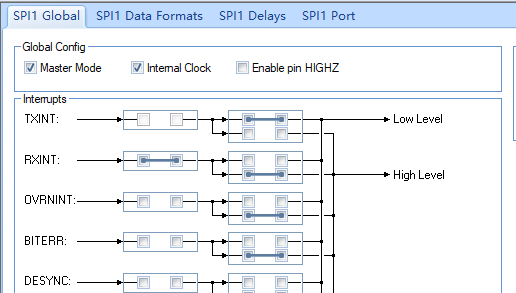

But not available in HalCoGen

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Transmit Buffer Empty Interrupt

But not available in HalCoGen

Hi Hongbo,

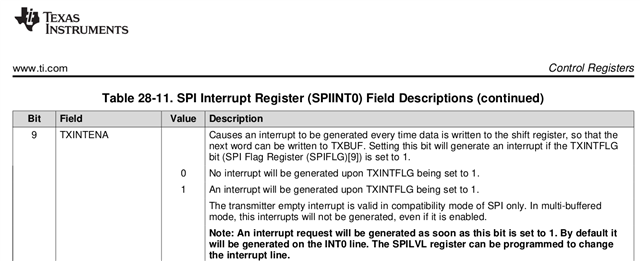

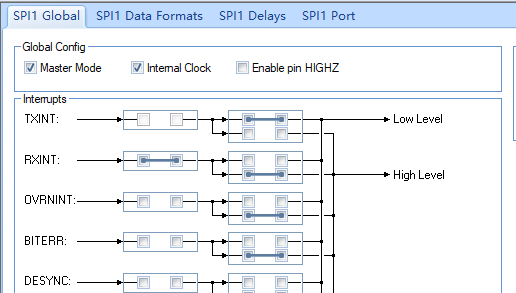

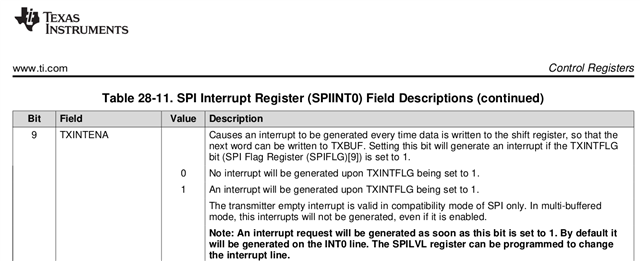

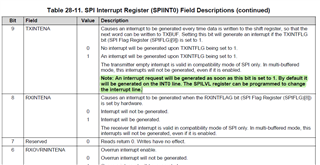

According to above data, the TXINT is generated as soon as it is enabled. So that means the TXINT bit should need to be SET only after all the initializations are completed right?

If we SET this bit during initializations, this will create interrupt immediately without any proper SPI initializations and this makes the SPI behavior unpredictable. And also, after initializations completed, we don't get TXINT again as we already processed the TXINT in initializations itself2.

Due to these reasons, they didn't provide chance to enable TXINT in HALCoGen. It should always need to be enabled after initializations.

You can also refer below thread:

(+) SPI4 TXINT in Halcogen for TMS570LS1224 - Arm-based microcontrollers forum - Arm-based microcontrollers - TI E2E support forums

--

Thanks & Regards,

Jagadish.