Hi Team,

There's an issue from the customer need your help:

、

、

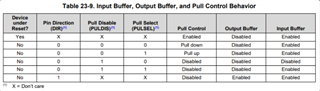

Configure according to Table 23-9, disable the input buffer of pin pin[n]. When N2HET is running, using the PCNT command can still capture the actual running level width on pin[n] .

Thanks & Regards,

Ben