Hello IT-Support,

i think the Build-in Self-test functionality is insufficient documented.

Additional it is a Build-in Self-test when a Core test the other Cores and not itself?

There is no documentation how the Build in Self-Tests work exactly. How the PBIST procedure work exactly?

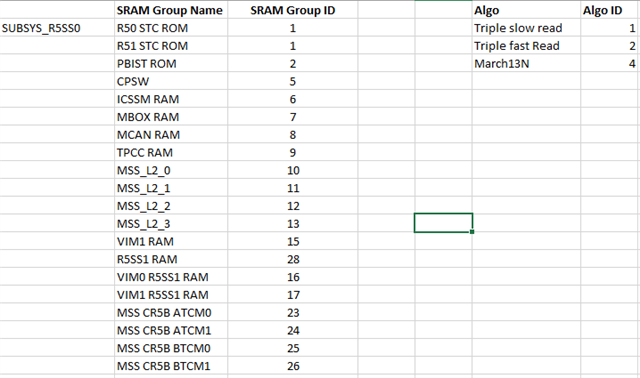

It can only use the fixed defines in sdlr_soc_pbist.h (like: SDL_PBIST2_ALGO_BITMAP_0) to make a config setup (with the PBIST_TestHandle_t structure) like in the examples.

There is no explanation (in API, code) which fixed defines (PBIST2) are for which instance (found out with spruim2g.pdf - Table 5-838).

There is no explanation how to setup this structure correct.

What is important to consider, when i want to use the BIST?

Can I change the fixed defines (like SDL_PBIST2_ALGO_BITMAP_0) ?