To Expert,

I am currently working on activating R5FSS0_1, R5FSS1_0, and R5FSS1_1 in SW where only R5FSS0_0 operates.

Through the SBL example, I understood how to load data from External Flash to RAM and then operate the Core through the SOC_rcmCoreR5FUnhalt function.

Therefore, it is assumed that all necessary data has been loaded into OCRAM.

However, I have a few questions about this:

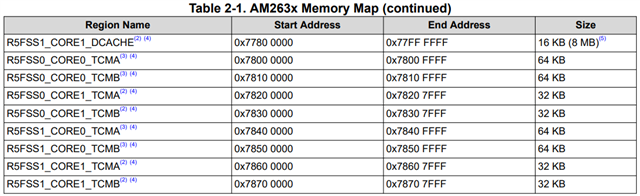

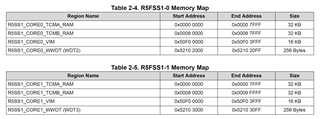

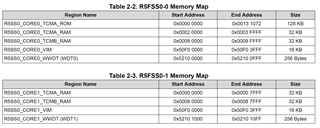

1. I understand initializing TCMA with functions like SOC_rcmStartMemInitTCMA. So how do I write data to TCMA after initialization? I understand that TCMA can only be accessed by each core. Is there another way?

2. Vector seems to be in TCMA, does it act as an EntryPoint? (When you load multi-core imange when debugging SBL, the entry point is set to 0 for the images corresponding to R5FSS0_1, R5FSS1_0, and R5FSS1_1.)

3. Can't I put the Core into a Halt state for testing?

Please reply for a lot of help in development.

Jiung Choi