Part Number: TM4C1290NCPDT

For a legacy system upgrade, We are interfacing a TM4C1290 to a FPGA, and two duart chips. We are using address decoding for the chip selects. The duarts are provided by a tl16c752.

We were initially looking at the GPIO mode, but discovered the timing would not match the read/write requirements of the duart.

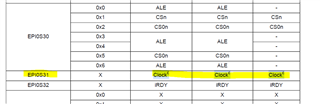

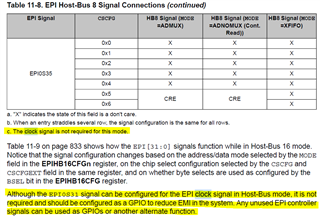

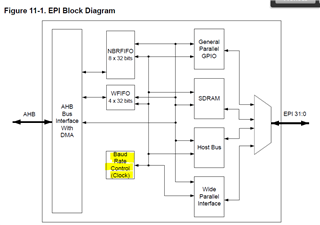

If we use the Asynchronous Host mode, can we output the clock for use externally, would this still be in conformance with the timing of read/write/data/address line changes?

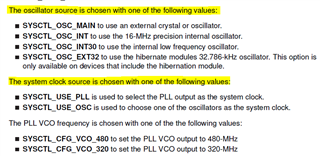

The System clock is an external clock and the EPI is set to use this unmodified. What is the expected propagation delay from input to output?