Hello,

I am a bit confused on how to catch and signal failures detected by LPOCLKDET and the PLL slip detector.

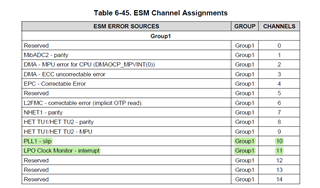

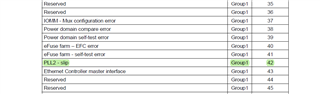

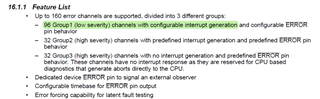

Besides reading the Global Status Register (GLBSTAT), do they trigger an ESM interrupt?

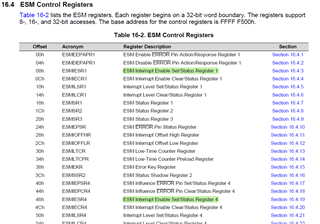

If yes, how to configure the LPOCLKDET and the PLL slip detector to generate an ESM interrupt? Do you have an example?

Thanks,

Marcio.