Other Parts Discussed in Thread: HALCOGEN

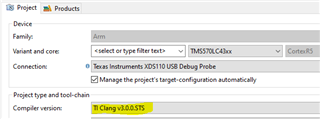

I am trying to compile and link a project with the tiarmclang. For some reason the .invetcs section always ends up with size 0. The project should use gnu assembly syntax.

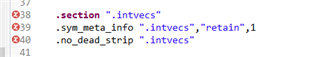

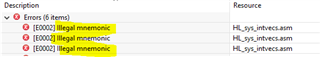

Here is the assembler code that defines the interrupt vectors.

.section ".intvecs"

.sym_meta_info ".intvecs","retain",1

.no_dead_strip ".intvecs"

.arm

resetEntry:

b _c_int00

undefEntry:

b undefined_instruction_handler

svcEntry:

b supervisor_call_handler

prefetchEntry:

b prefetch_abort_handler

dataEntry:

b data_abort_handler

phantomEntry:

b phantom_interrupt_handler

irqEntry:

ldr pc,[pc,#-0x1b0]

fiqEntry:

ldr pc,[pc,#-0x1b0]

here is a part of the .map file

architecture: arm

start address: 0x0000a380

Program Header:

LOAD off 0x00000034 vaddr 0x00000000 paddr 0x00000000 align 2**2

filesz 0x00000008 memsz 0x00000008 flags r--

LOAD off 0x00000040 vaddr 0x00000020 paddr 0x00000020 align 2**4

filesz 0x00010fa0 memsz 0x00010fa0 flags r-x

LOAD off 0x00010fe0 vaddr 0x0800b730 paddr 0x00010fc0 align 2**4

filesz 0x00000f30 memsz 0x00000f30 flags r-x

LOAD off 0x00011f10 vaddr 0x00011ef0 paddr 0x00011ef0 align 2**3

filesz 0x00001070 memsz 0x00001070 flags r--

LOAD off 0x00012f80 vaddr 0x08002000 paddr 0x08002000 align 2**2

filesz 0x00000000 memsz 0x0000972e flags rw-

LOAD off 0x00012f80 vaddr 0x0800c660 paddr 0x0800c660 align 2**3

filesz 0x00000000 memsz 0x00000800 flags rw-

LOAD off 0x00012f80 vaddr 0xf0400000 paddr 0xf0400000 align 2**0

filesz 0x00080000 memsz 0x00080000 flags r--

Dynamic Section:

Sections:

Idx Name Size VMA LMA Type

0 00000000 00000000 00000000

1 .intvecs 00000000 00000000 00000000

Any ideas how to fix this?