Hello, we are using SDK 08.06 and LTS2.1.3

I just noticed an alignment-Problem with the ospi-functions when we are building in release (-Oz). In debug everything works. We use an external pSRAM via GPMC. I am not sure anymore, but I thought we found something which said it can only access 4 byte alignments. We also use the -mno-unaligned-access compiler option.

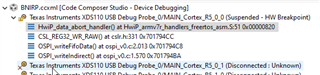

The abort happens here:

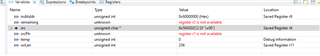

Taking a look at the variables in question:

it seem it accesses an address aligned with 2 and internally it casts from an uint8_t to an uint32_t (which I think is dangerous anyway everytime, but I know the ARM allows unaligned access, but not for our psram...)

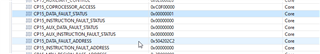

Also I checked the fault registers:

The 1 means alignment fault following the arm documentation:

https://developer.arm.com/documentation/ddi0406/b/System-Level-Architecture/Protected-Memory-System-Architecture--PMSA-/Fault-Status-and-Fault-Address-registers-in-a-PMSA-implementation/Fault-Status-Register-encodings-for-the-PMSA?lang=en#Bcejbahe

So... what would be the options here? Currently I'll try to align every data we have to 4 but I do not think that's the useful option.

Edit: I moved the memory to copy into internal SRAM. But still the abort happens.It happens right after calling this.

As you can see the srcPtr shows to an address aligned to 2. And this only happens with -Oz (and debug-symbols for the screenshot). If I build a Debug-elf with -Og the adresses are also aligned to 2 but this somehow works.

Debug generates the following assembly:

while release generates:

right after an assembly step the application runs into the abort.

What could we have done wrong?

Best regards

Felix