Hello,

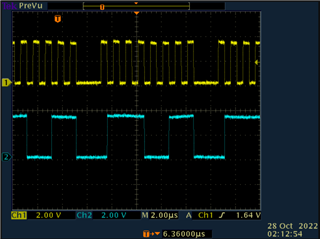

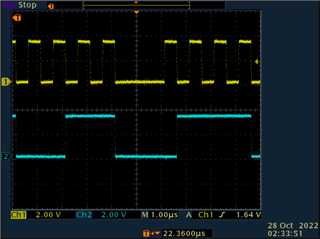

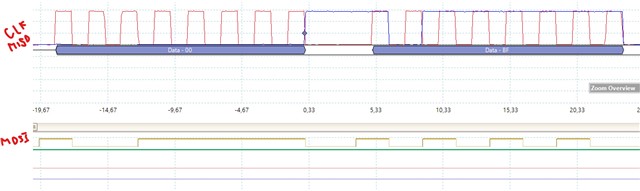

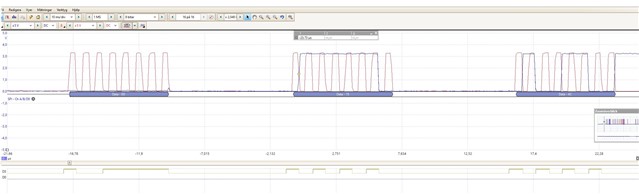

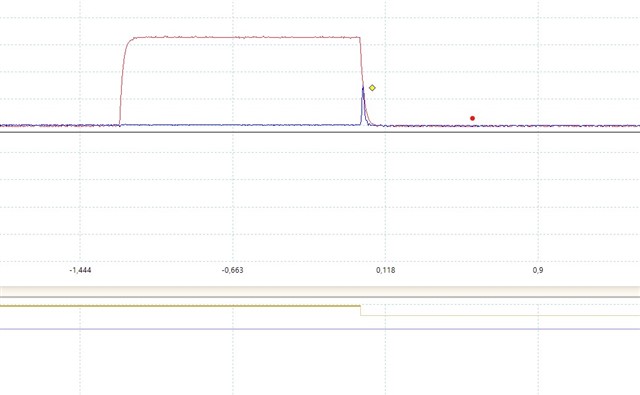

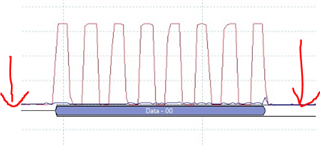

We use SS2 as SPI and try to configure, write and read data from an external flash memory. Everything is working fine but sometimes we read wrong data on MISO from the flash chip. For ex, if we expect 01 02 03 04 05 06 there can be either all data is 00 or some random numbers.

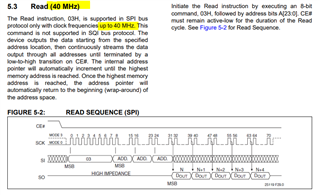

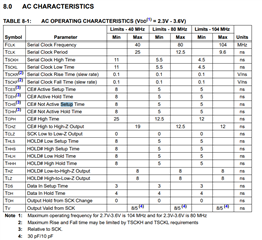

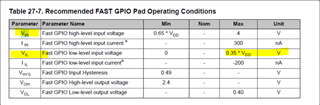

We tried to switch to SS3 but the same problem is still there. We have verified that the clock signal is correct and that the data on MOSI is correct but the flash chip is not responding what we expect occasionally. Can it be that the flash chip is not compatible with this CPU. We use a flash SST26VF064B from another family.

Thank you in advance!

Regards,

Gergana

.

.