Other Parts Discussed in Thread: SYSCONFIG

Hello MSP team,

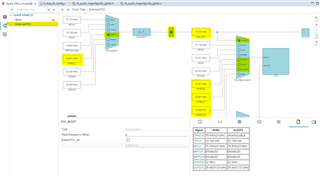

my customer is currently trying to connect an external clock with 37.125MHz to the MSPM0G HFCLK input.

MSPM0G3507 Rev B, SDK 1.10.01.05

The problem is that the external HFCLK is not recognized by the PLL, after configuration the CLKSTATUS register has the value of 0x20107800 and therefore not HFCLK was recognized.

They have already checked the clock and it is working fine and is up during booting.

After investigation there were some issues:

1. Incorrect pin configuration: DL_GPIO_initDigitalInput(GPIO_HFCLKIN_IOMUX); instead of DL_GPIO_initPeripheralInputFunction(GPIO_HFCLKIN_IOMUX, GPIO_HFCLKIN_IOMUX_FUNC);

2. The generated DL_SYSCTL_SYSPLLConfig structure is not matching. Is: DL_SYSCTL_SYSPLL_INPUT_FREQ_8_16_MHZ ; should be: DL_SYSCTL_SYSPLL_INPUT_FREQ_32_48_MHZ

3. It is not possible to output the clock to CLK_OUT or be counted by FCC.

Clock tree is activated.

Is there any special configuration necessary to use an external clock on MSPM0G?

Thanks in advance.

Regards

Manuel