Part Number: TM4C1231E6PZ

Hi Team:

My customer using TM4C1231E6PZ, and we have a question would like to ask. The TM4C1231E6PZ chip uses SPI communication and is used as a slave.

How to judge that the host has completed sending data? Sent via DMA between master and slave.

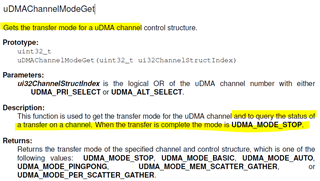

Can it be determined using the functions uDMAChannelIsEnabled(MASTER_SSI_UDMA_RX_CHANNEL) and SSIBusy(MASTER_SSI_BASE)?

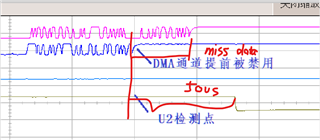

because we found the following issues:

The program code is as follows:

tem1 = (_Bool)((uDMAChannelIsEnabled(MASTER_SSI_UDMA_RX_CHANNEL))||(uDMAChannelIsEnabled(MASTER_SSI_UDMA_TX_CHANNEL)))

if((tem1 == (_Bool)false) )

{

uDMADisable();

……………………

}

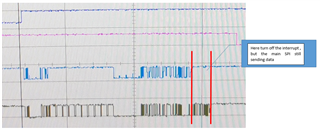

It was found that the main SPI was still sending data, but the " if “ was true and the slave SPI turned off the interrupt.

As shown below, please help confirm whether there is a problem with customer`s program configuration? Please provide reference configuration. tks ~

for more details: