I looked at the example adc_udma_pingpong and have questions about it:

1. why do I need to enable burst mode on a channel with a sequence? Or in other words, what advantages does this give me?

// // Set the USEBURST attribute for the uDMA ADC0 channel. This will force // the controller to always use a burst when transferring data from the // TX buffer to the UART. This is somewhat more efficient bus usage than // the default which allows single or burst transfers. // uDMAChannelAttributeEnable(UDMA_CHANNEL_ADC0, UDMA_ATTR_USEBURST);

2. there is always a sample transmitted via dma. In the data sheet on page 801 I see a FIFO block with 4 cells. Can this be used to transfer 4 finished samples via dma?

Then the burst mode would make sense for me again.

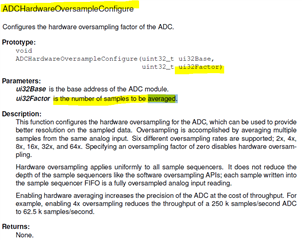

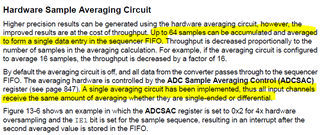

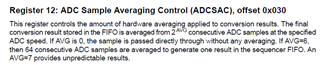

3. on page 807 in the data sheet it is about hardware sample averaging. This 4 cell FiFo is also shown there. 4 samples are combined and divided by the number of samples. I am still unsure with which sample rate an averaged sample was sampled. I have the function; ADCClockConfigSet() and about ADCSequenceConfigure() I can set a timer with a fixed frequency. I think I need an example.