Hello,

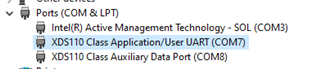

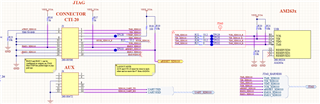

I have a new board that I am trying to bring up using the XDS110 Debug Probe.

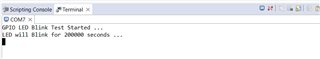

I have the following connections and unable to get the Sitara to communicate over the UART interface when the Sitara is set in UART mode. UART pints are routed to UART0 A7/A6 balls.

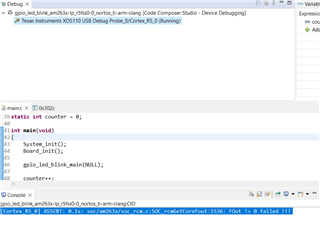

My first thoughts are does the Sitara need to be flashed over JTAG or configured in any way before it will start to talk in UART or should I see the "cccc" being printed out of the box? JTAG seems to be working fine I was able to load code using the Dev Boot Mode.