Hi BU experts,

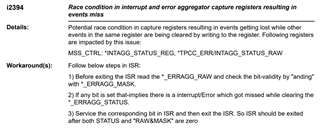

In errata notes, there is an advisory about interrupt event missing:

I want to check with you:

1). I can't find register MSS_CTRL: *INTAGG_STATUS_REG, *TPCC_ERR/INTAGG_STATUS_RAW in Register Addendum. Please clarify the registers with this issue.

2). Is the workaround implemented in our SDK? Or need customer to implement it by themselves.

Regards,

Will