Other Parts Discussed in Thread: LP-AM263

Hey Sitara MCU team,

I have a customer working on their HW implementation for a new design based on the AM2634 and they noticed a discrepancy between the recommended decoupling circuitry in the HW Design Guide (SPRABJ8A) versus the actual Launchpad design (LP-AM263).

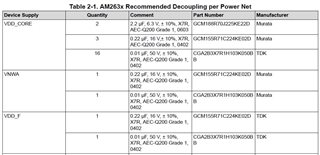

One specific discrepancy that I can point out is the guidance provided for handling VDD_CORE. In Table 2-1 of the design guide it recommends 16x 0.01uF, 3x 0.22uF, and 2x 2.2uF capacitors for VDD_CORE but if you look at the same document in Figure 2-5 along with the actual LP-AM263 PROC111E2 schematic you'll see that the actual decoupling capacitors used on this node (VDD_AM263_1V2) are different. Similar discrepancies can also be seen for other rails like VNWA and VDD_F. See below for reference!

Our question is...which design guidance is correct and should be followed?

1.2V Decoupling Circuitry on LP-AM263:

1.2V Decoupling Recommendation from HW Design Guide:

Thanks for your help with clearing this up!

Best regards,

Matt Calvo