Other Parts Discussed in Thread: HALCOGEN

Hello,

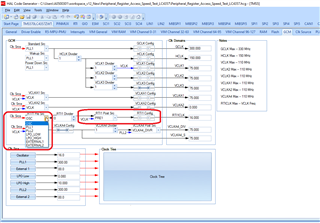

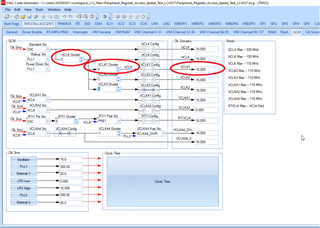

What are the clocks values before the systemInit() routine (created by Halcogen) is called, that is, before the PLL and clocks are configured?

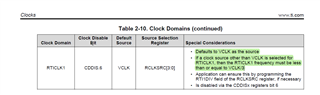

Can watchdog be enabled before the systemInit() ? If yes, what is the value of RTICLK1? Does the watchdog needs to be reconfigured after systemInit()?

Best regards,