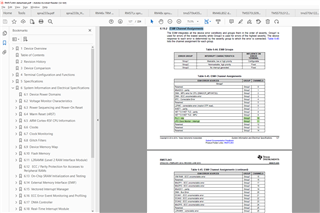

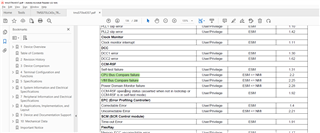

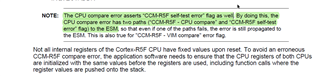

Where I can find the a detailed description of each ESM channel for RM57L843BZWTT, including the bit number in the ESM registers ESMIESR1, ESMIECR1, ESMILSR1, ESMILCR1, ESMSR1, ESMSR2,

ESMSR3, ESMSSR2, ESMIEPSR4, ESMIEPCR4, ESMIESR4, ESMIECR4, ESMILSR4, ESMILCR4, ESMSR4, ESMIEPSR7, ESMIEPCR7, ESMIESR7, ESMIECR7, ESMILSR7, ESMILCR7, ESMSR7 and the value of ESMIOFFHR and ESMIOFFLR?

Beadt regards,

Marcio.