Hi Experts,

So I wanted to implement a multicore project to use CPSW and ICSSG LWIP stack together. The motivation is as follows:

- Core r5Fss0-0: Implements the example "enet_lwip_cpsw", source: enet_lwip_cpsw (ti.com) @ MCU+ SDK for AM243x (09.00.00.35)

- Core r5Fss0-1: Implements the eaxmple "enet_lwip_icssg", source enet_lwip_icssg (ti.com) @Industrial Communications SDK for AM243x (09.00.00.03)

I read the SDK documentation on the need to allocate resources and change the linker commands, if one wants to wortk with multiple cores. I have made the neccessary changes in system config and the linker scripts.

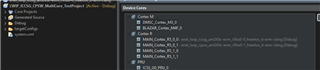

Consequently I created a CCS 'System' project as follows:

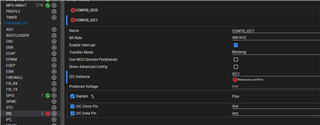

Important to mention here is that the two examples run on the two desired cores separately, however when I try to build/complie the combined multicore project, I get errors saying that there is resource conflict between the the two cores as shown in the snippet below:

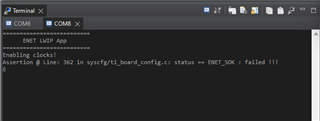

I tried to assign the other I2C instances for e.g. I2C_2 and I2C_3 also the MCU domain instances, this change enabled thge build to be successful but then at runtime the CPSW based app cannot read the MAC address from EEprom and I get the following assert failure:

Also according to the user guide it can be intrepreted that I2C0 and I2C1 are the correct instances:/resized-image/__size/320x240/__key/communityserver-discussions-components-files/908/pastedimage1699372110278v1.png

What am I missing? Is there a different approach that needs to be followed. Could it be that some driver change is required?

Kindly advise.

Many thanks and best regards,

Shobhit