Part Number: AM2634

Other Parts Discussed in Thread: AM2631

Hi TI Expert,

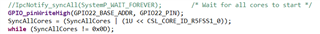

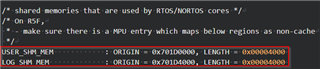

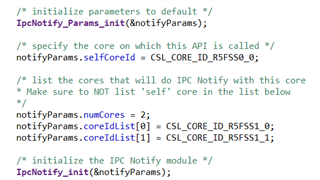

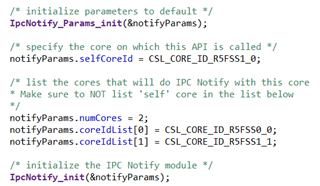

I am using a global variable in user shared memory region (at address 0x701D0000) which is bit masked by multiple cores.

Sometimes while running in NO BOOT mode, I have observed that the variable at address 0x701D0000 gets overwritten by different cores instead of bit masking. Specially when I flash the application SW into QSPI flash, the application SW does not boot up as I believe the execution gets stuck checking for the bit masked variable to be a specified value.

Could you please advise me how to resolve this issue? Are there MPU settings to block memory overwriting from other cores? or changes required in RAM/cache or bootloader?

Thanks in advance!