Other Parts Discussed in Thread: SYSCONFIG

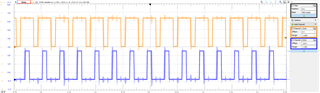

I have configured a timer in PWM mode using SYSCFG, and am trying to understand what configuration it's setting up for me. From the code in DL_Timer_initPWMMode(), I can see that a CENTER_ALIGNed timer is configured to set the output high when counting up and low when counting down (assuming I've interpreted (DL_TIMER_CC_CUACT_CCP_HIGH | DL_TIMER_CC_CDACT_CCP_LOW) correctly). In my mind, this would be consistent with a counter in up-down mode, with the center-alignment applied to the center of the high-period. It also matches the drawn use-case in section 23.2.5.2.2 which demonstrates center-aligned PWM using up-down counting.

However, later in that function it looks like the CVAE bits in CTRCTL are being cleared, which the reference manual describes as operating in down-up mode, which I think would actually center-align about the low-period of the pulse.

Is the intention of the SYSCFG to set the PWM up in up-down mode or down-up mode when using SYSCFG in this way?