Other Parts Discussed in Thread: HALCOGEN

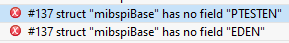

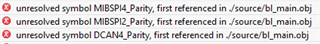

When I compile the demo for this processor, there are references in parity_functions.c to undefined test registers canREG1->TEST, mibspi1->PTESTEN, mibspi3->EDEN. These are defined in the demos for other TMS570 processors and for RM42x,RM46x, RM48x. Do these registers exist in TMS570LC4357 or should these tests be excluded?