Hi,

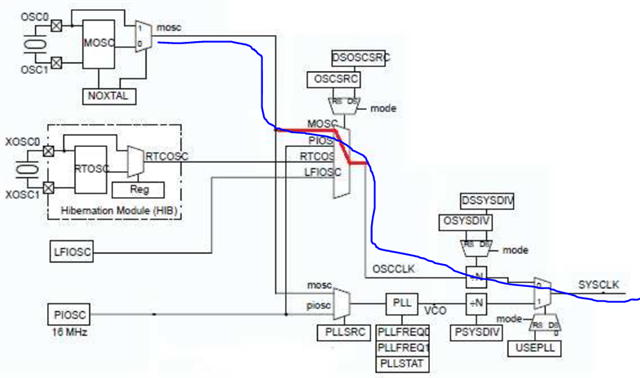

My customer wants to use 20MHz MOSC clock as SYSCLK source. SYSCLK is also 20MHz.

Clock phase for both clocks (MOSC and SYSCLK) must be aligned.

The customer wants to use MOSC as SYSCLK source with PLL bypass, but the errata SYSCTL#23 says it may causes "a bus fault on reset".

Question#1:

The customer tested above usecase and it works fine without any issues.

What does "a bus fault" here exactly mean?

Are there any other conditions to cause a bus fault?

Question#2:

Suppose PLL is used as MOSC as PLL source, then the clock is multiplied by N and divided by N, SYSCLK frequency is configured as 20MHz.

This works as workaround, but in this case, clock phase of MOSC and SYSCLK is still aligned?

The customer afraid there are N different combination of phases.

Thanks and regards,

Koichiro Tashiro

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.