Other Parts Discussed in Thread: AM2634

Hi, experts,

Customer encountered a soft reset issue, that occasionally AM2634 can NOT restart normally after triggering a soft reset in application code.

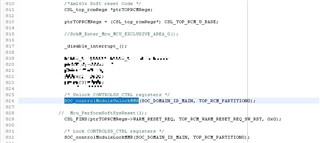

Below is one captured abnormal status. When the expected reset not observed, customer got below screenshot by connecting JTAG and found the PC is 0x000039F6. But from the map file, there is no application code placed in this address. Is it possible that the running was stuck in ROM code?

Customer uses Mcu_PerformReset() to trigger soft reset in project using MCAL. I have done some tests with Mcu_PerformReset() with example from MCAL package, but can NOT reproduce the issue.

Please help to guide the ways to find the root cause, what may be the reason.

Thanks.