Other Parts Discussed in Thread: TM4C123GH6PM, LM3S2965

Hello all!

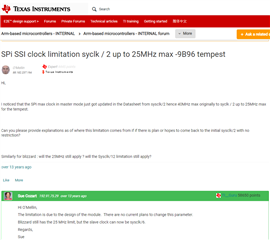

Whilst debugging a rather insidious SSI "feature" I stumbled upon what might be an error in the TM4C123 datasheets (I have checked a few and they all have the same data). Specifically, in the Bitrate Generation section it states that for Master mode, the SSI Baud rate must be no faster than half of SysClk and no more than 25MHz. This is "confirmed" in the Spec section where it shows a minimum cycle time of 40ns. This looks like it *could* be a left-over from earlier LM3S parts which were clocked at 50MHz.

An investigation of the TivaWare source code reveals no additional checks beyond the SysClk/2 test, so TivaWare will quite happily accept up to 40MHz. Indeed, I can confirm that the TM4C123GH6PM will happily runs its SSI at 40MHz.

Further support for this theory of an incorrect value in the datasheet comes from the TM4C129 datasheets. These have the same SysClk/2 limitation but then state a maximum SSI Baud rate of 60MHz (which is indeed half of the rated 120MHz SysClk). The spec section also shows a minimum cycle time of 16.66ns. It is true that the TM4C129 devices have a revised SSI core, so it is still possible that the TM4C123 genuinely "should" not be used faster than 25MHz (and the fact that it does work at 40MHz is more luck than design), but if it is indeed an error in the datasheet, then perhaps it can be added to the Datasheet Errata ?

Cheers,

Pat.