Hi Team,

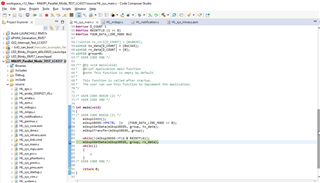

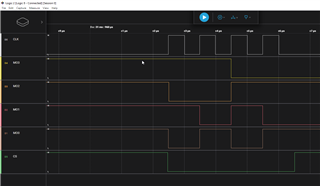

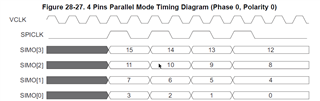

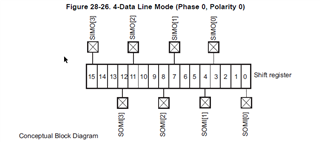

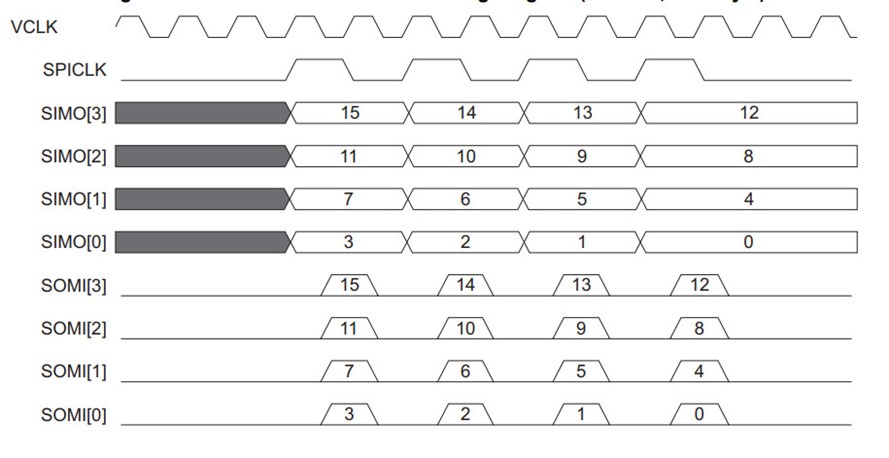

The MibSPI module outputs 15,14,13,12 for 4-wire 16-bit data instead of 15,11,7,3bits.

The customer would like to know why this model is only supported? Is there a way making it possible to switch to SIMO[3:0] to output 15, 11, 7, 3 bits, respectively?

Could you help check this case? Thanks.

Best Regards,

Cherry