Other Parts Discussed in Thread: UNIFLASH

Hi,

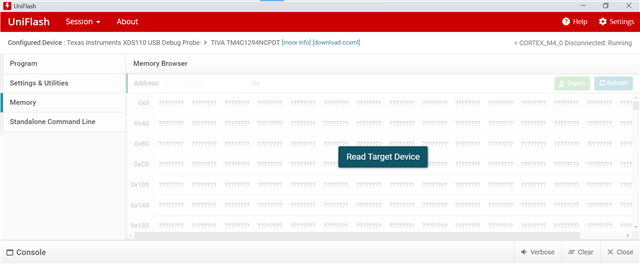

I'm using a TM4C1294NCPDT with an XDS110 debugger. I was curious about the presence of code in Flash memory. So I attempted to read memory using Uniflash. When I pressed the "Read Target Device" button, my application became corrupted for a short period of time. Interruptions did not work in that short amount of time. As a result, I need to understand the actions from Uniflash to the TM4C microcontroller.

Please assist me in understanding the concept and operation of the flash read in Uniflash using the xds110 debugger and clearing these doubts.

1. What impact does this have on my application code?

2. What happens when Uniflash and Microcontroller interact?

3. Is the flash freezing?

4. Why aren't the interrupts executed in the particular time?