Part Number: AM2432

Hello there,

We have some questions regarding using SDL for ECC on TI Sitara AM2432 Arm-Cortex M4 core:

- In the ECC SDL example, SDL_ECC_AGGR1(Value 3) is passed as memtype for ECC init(SDL_ECC_init) API. Can you provide more information on this interface ?

- Why AGGR1 is passed as memtype?

- How these memtypes are linked with the physical memory?

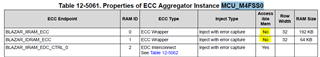

- Our objective is to perform RAM test on M4 core. If we are selecting memtype as MCU_M4FSS0(SDL_MCU_M4FSS0_BLAZAR_ECCAGGR) and we wanted to perform test on ECC wrappers, How can we test it? In TRM document, this memory is shown as inaccessible.

- In the TRM document(Refer: Table 12-5051) we could see 6 ECC endpoints are connected to ECC AGGR1. But in the example during ECC Initialization API( SDL_ECC_init), it selects only 2 below given ECC end points.

IAM64_MAIN_INFRA_CBASS_MAIN_0_AM64_MAIN_INFRA_CBASS_IK3VTM_N16FFC_MAIN_0_VBUSP_P2P_BRIDGE_IK3VTM_N16FFC_MAIN_0_VBUSP_BRIDGE_BUSECC & IAM64_MAIN_INFRA_CBASS_MAIN_0_AM64_MAIN_INFRA_CBASS_MAIN_SYSCLK0_4_CLK_EDC_CTRL_CBASS_INT_MAIN_SYSCLK0_4_BUSECC).

What about other ECC endpoints? - What is the exact difference between SDL_ECC_init API and SDL_ECC_initMemory API ?

Our understanding is SDL_ECC_initMemory has to be called multiple times to initialize multiple ECC endpoints where as we can call SDL_ECC_init just once to initialize multiple ECC endpoints. Please clarify - What is the exact difference between SDL_ECC_injectError API and SDL_ECC_selfTest API ? Please clarify below points.

- Can we use SDL_ECC_selfTest API during run time. Our understanding is that as it’s a blocking call it has to be used during startup only.

- Our understanding is that SDL_ECC_selfTest API provides ‘number of retries’ and ‘Interrupt handling mechanism’ which needs to be added additionally in case of SDL_ECC_injectError API by the user application.

- In the example of ECC, it is clearly shows how to inject error on ECC Interconnect using SDL_ECC_injectError API. Is it the same way for ECC Wrappers?

- Can you provide us more information on different Checker ‘Group ID’ and ‘Checker Type’?

- Parity, Redundant and Error Detect and Correct.

- Do we need to inject error on each and every Checker Group IDs and verify?

Thanks,

Luis