Other Parts Discussed in Thread: HALCOGEN

I am currently using SPI1 for some communications. The device I am talking to requires the CS to be held active (low) while I write a buffer. However, using DMA I seem to lose the ability to control the SPI CS hold. I had to modify the halcogen code slightly so can send a specific 3 bytes before I send the buffer each time and keep the CS active.

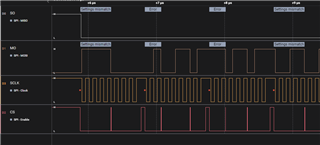

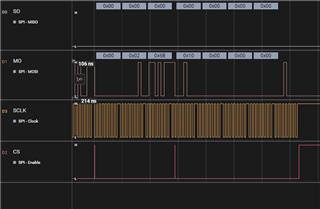

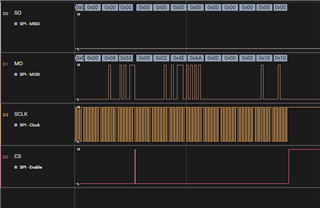

In the image below it shows the CS line toggling after each 8-bit transmission, which is what I want to prevent. Everything else seems to work okay.

Simply I want the CS line to stay active low for the whole DMA transfer. So here are my questions:

1. Is there a way to use the SPI mode pin for CS along with DMA to control the CS to remain low for the entire block transfer? Or am I going to have to utilize a GIO pin instead?

2. Would switching to mibSPI be a better alternative? Does that provide more control of the CS pin with DMA?