Other Parts Discussed in Thread: SYSCONFIG

Hello! TI,

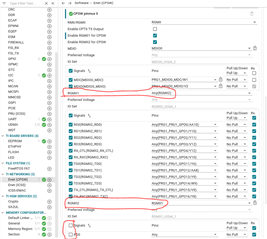

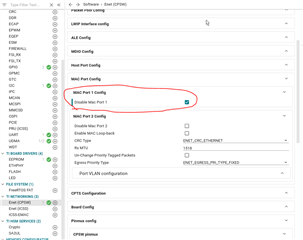

We are trying to use the CPSW example with RGMII2, but it does not work.

Using the example, we forcibly assigned an IP and checked Link Up and Network Up in the log.

However, no packets are received or transmitted.

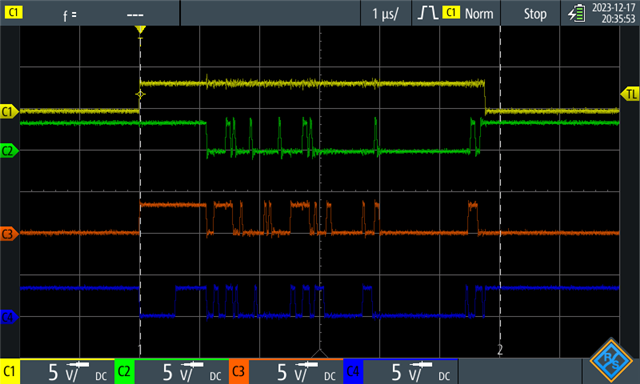

When we check the port sent from DP83869 to AM2434, we see the Rx signal and RXC signal, but there is no content in AM2434's UDMA memory for ENET.

Please help us.