Other Parts Discussed in Thread: LP-AM243, SYSCONFIG

Hi all TI experts,

I am currently using a product board manufactured by our company, featuring the AM2431 as the main IC. Our board connects the AM2431 to a Realtek Ethernet switch IC via the RGMII interface. We are encountering issues in communicating with the switch IC.

I have previously tested the 'Enet Layer 2 CPSW Example' from the SDK on the LP-AM243 development board and successfully got it to work. However, the LP development board uses the CPSW3G to configure one host port and two MAC ports, connecting externally to two PHYs via MDIO/MDC. Our product board, on the other hand, connects only to a single switch IC, i.e., one PHY. Therefore, I believe it should be configured as CPSW2G, which means one host port and one MAC port. Additionally, my switch IC needs to be initialized through the MDIO/MDC interface. Here are my questions:

- In SysConfig, under Enet(CPSW) -> Pinmux config, since I am connecting to only one switch IC, I need only one PHY. Does this mean I should disable the signals for RGMII2 and retain only RGMII1?

- As I require only one MAC port, in SysConfig, under Enet(CPSW) -> MAC Port Config -> MAC Port2 Config, should I select 'Disable Mac Port 2'?

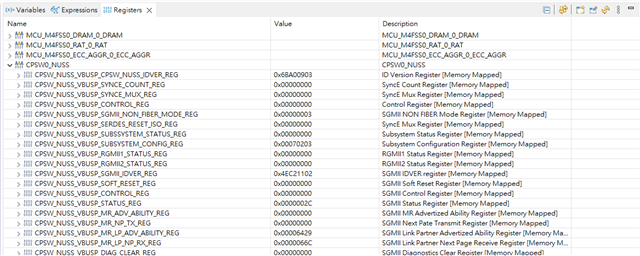

- According to the SDK documentation, specifically the 'Networking->Enet-LLD->Ethernet PHY Integration Guide' and 'Networking->Enet-LLD->Enet Migration Guide', I need to create a PHY driver for my switch IC at the corresponding address. I have also created my custom_board_config.c file, as I checked the option in SysConfig under Enet(CPSW)->Board Config. However, my PHY still fails to connect. My code is primarily a modification of the 'Enet Layer 2 CPSW Example'. The log stops after executing 'cpsw-3g: Waiting for link up...'. I suspect this might be due to my switch IC not undergoing the initialization process, as I don't see the program executing my written PHY driver. Even in debug mode, I couldn't see the program reaching that part, leaving me uncertain if there was a configuration error on my part.

Can someone guide me on what corrections I can make, or are there other documents I can refer to?

Best regards,

Larry