Hi, we are evaluating the CPSW peripheral on AM263Px for a gigabit application and are struggling getting the Layer 2 CPSW example to work. Here is my setup:

MCU+ SDK v9.01.00.20

AM263Px Control Card rev E2 with 180 pin HSEC docking station

Booting in OSPI mode with SBL NULL flashed

Using "Enet Layer 2 CPSW" example from MCU+ SDK (no changes, compiled in release mode)

Loading binary to ControlCard via CCS+JTAG

Direct Ethernet connection between ControlCard and development computer

Using ColaSoft Packet Builder to send packets (ARP packet type with Destination Address set to match ControlCard MAC and Source Address set to match development computer MAC)

Problem:

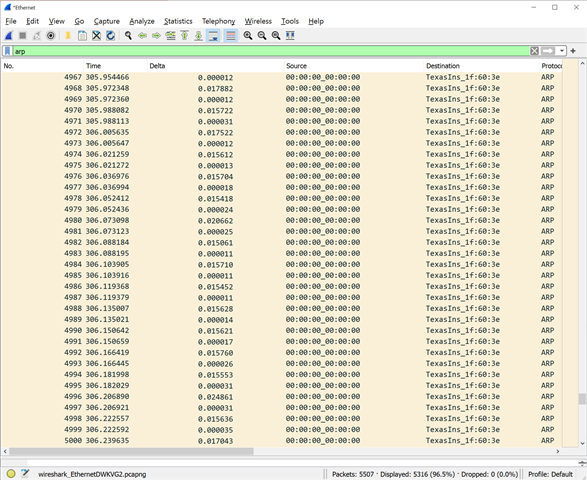

When running the "Enet Layer 2 CPSW" example, after sending ARP packets from development machine to ControlCard (using ColaSoft Packet Builder per MCU+ docs), the CPSW statistics always show zero. Wireshark shows the ARP packets from PacketBuilder are transmitted but the development computer does not receive any reply from the AM263Px ControlCard.

Here is the output from the AM263Px CC:

INFO: Bootloader_socLoadHsmRtFw:82: Device Type : HSFS

[HSM_CLIENT] New Client Registered with Client Id = 0

INFO: Bootloader_socLoadHsmRtFw:84: HSMRT Size in Bytes : 23875

INFO: Bootloader_socLoadHsmRtFw:97: hsm runtime firmware load complete ...

Starting NULL Bootloader ...

INFO: Bootloader_runCpu:155: CPU r5f1-1 is initialized to 400000000 Hz !!!

INFO: Bootloader_runCpu:155: CPU r5f1-0 is initialized to 400000000 Hz !!!

INFO: Bootloader_runCpu:155: CPU r5f0-1 is initialized to 400000000 Hz !!!

[BOOTLOADER_PROFILE] Boot Media : undefined

[BOOTLOADER_PROFILE] Boot Image Size : 0 KB

[BOOTLOADER_PROFILE] Cores present :

[BOOTLOADER PROFILE] System_init : 70us

[BOOTLOADER PROFILE] Drivers_open : 40us

[BOOTLOADER PROFILE] LoadHsmRtFw : 31939us

[BOOTLOADER_PROFILE] SBL Total Time Taken : 56138us

NULL Bootloader Execution Complete...

INFO: Bootloader_loadSelfCpu:207: CPU r5f0-0 is initialized to 400000000 Hz !!!

INFO: Bootloader_runSelfCpu:217: All done, reseting self ...

==========================

Layer 2 CPSW Test

==========================

Init all peripheral clocks

----------------------------------------------

Create RX tasks

----------------------------------------------

cpsw-3g: Create RX task

Open all peripherals

----------------------------------------------

cpsw-3g: Open enet

EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:0 From 4 To 2

Init all configs

----------------------------------------------

cpsw-3g: init config

cpsw-3g: Open port 2

EnetPhy_bindDriver: PHY 0: OUI:080028 Model:0f Ver:03 <-> 'dp83869' : OK

PHY 0 is alive

Attach core id 0 on all peripherals

----------------------------------------------

cpsw-3g: Attach core

cpsw-3g: Open DMA

initQs() txFreePktInfoQ initialized with 16 pkts

cpsw-3g: Waiting for link up...

Cpsw_handleLinkUp: Port 2: Link up: 1-Gbps Full-Duplex

MAC Port 2: link up

cpsw-3g: MAC port addr: 70:ff:76:1f:60:3e

Enet L2 cpsw Menu:

's' - Print statistics

'r' - Reset statistics

'm' - Show allocated MAC addresses

'x' - Stop the test

s

Print statistics

----------------------------------------------

cpsw-3g - Port 2 statistics

--------------------------------

I verified SW14/15/16 on the ControlCard are all in the default 'OFF' position which should route CPSW RGMII2 to the onboard PHY.

Any ideas?