Part Number: AM2634

Hello Team,

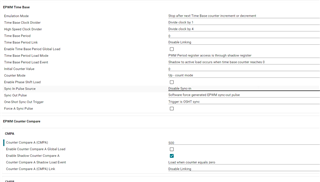

I have configured 3 ADC units with same hardware trigger (EPWM SOC hardware trigger). And Each ADC Unit contains 6 channels each with sample window 64.

We are using clock configurations from gel file only. and ADC prescalar value selected is ADC_CLK_DIV_8_5 for all 3 units.

The taken for the conversion between the pwm interrupt to start of ADC interrupt is about 6.77us.

And one mor point, this 6.77us is irrespective of the number of channels configured. if each unit contain 1 channel, that case also time is 6.77us only.

As per technical reference manual,

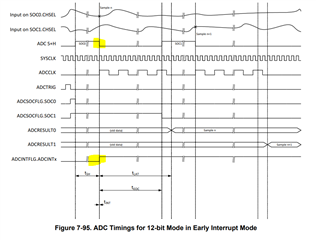

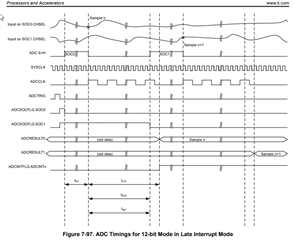

The time from pwm Interrupt (Hardware trigger) to start of ADC interrupt = (S+ H time) + Conversion time.

S+H time = 64*5ns = 320ns

conversion time = 11.5 times ADCCLK = 11.5 /(200Mhz/8.5) = 488.75ns

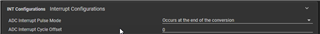

Since it is a synchronized conversion, interrupt will be generated at the end of acquisition window of SOC5. i guess after 6*320ns, right?

1. But why it is taking 6.7us to generate an ADC interrupt?

Could you please provide feedback for this?

2. Can we optimize the timing between PWM trigger and Start of ADC conversion? How it is possible?

Thanks and Regards

Aswathy J G